FPGA芯片在高速数据采集缓存系统中的应用

时间:08-19

来源:互联网

点击:

在高速数据采集方面,FPGA有单片机和DSP无法比拟的优势。FPGA的时钟频率高,内部时延小,全部控制逻辑都可由硬件完成,而且速度快,组成形式灵活,并可以集成外围控制、译码和接口电路。更最主要的是,FPGA可以采用IP内核技术,以通过继承、共享或购买所需的知识产权内核提高其开发进度。而利用EDA工具进行设计、综合和验证,则可加速设计过程,降低开发风险,缩短了开发周期,效率高而且更能适应市场。本数据采集系统就是基于FPGA技术设计的多路模拟量、数字量采集与处理系统。FPGA的IO端口多,且可以自由编程、支配、定义其功能,同时配以verilogHDL语言以及芯片自带的可定制模块,即可进行软件设计。FPGA的最大优点是可在线编程。此外,基于FPGA设计的数据采集器还可以方便地进行远程功能扩展,以适应不同应用场合的需要。

1 系统基本构架

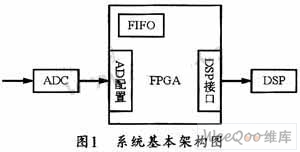

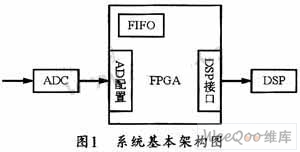

本文所设计的高速数据采集系统是某雷达信号处理系统的一部分,可用于雷达信号的预处理以及采集、缓存。本系统以高速FPGA为核心逻辑控制模块,并与高速ADC和DSP相连接。其系统基本架构如图1所示。

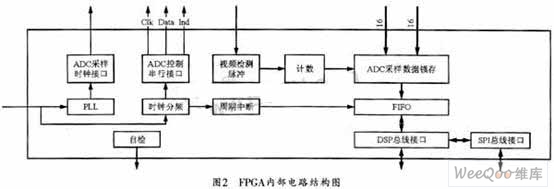

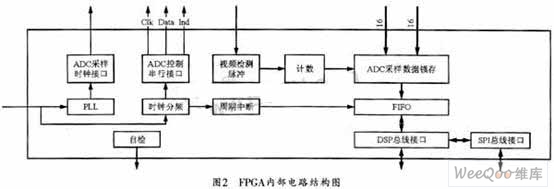

图1中的FPGA可用作数字接收机的预处理模块,该器件集成有PPL倍频、ADC控制接口、FIFO及其管理、SPI接口、DSP总线接口、状态和自检模块等。FPGA的内部结构功能框图如图2所示。

图2中的中断产生模块用于产生周期性中断,利用视频包络和100 MHz时钟可形成50 MHz的DMA同步传送时钟,然后通过外部口DMA方式将采样数据传送到DSP。ADC控制串行接口为通用三线串口,SPI总线接口实际上是一个串并转换器,可用于控制本振。本系统的DSP数据总线为64位宽度,地址为32位。

由于雷达信号接收机中的信号处理量大,信号复杂,因此,通过基于高速大容量FPGA芯片的实时数据采集系统可以很好的满足对信号预处理的需要。

2 芯片的选取

ADC是数据采集系统的核心,其性能指标往往是决定数据采集系统性能最关键的因素。本系统的中频频率为1125 MHz,带宽BW为250 MHz。ADC选用ATMEL公司的高速采样芯片AT84AD001本系统采用带通采样方式,其采样频率低于输人中频频率。但是ADC的输入带宽必须大于中频频率加二分之一带宽,AT84AD001的模拟输入带宽为1500 MHz,高于1125+125=1250 MHz,故可满足设计要求。AT84AD001的最高采样率为1000MHz,也可以满足系统要求。此外,AT84AD001的模拟输入、时钟输入和输出全部采用差分方式。设采样时钟频率fsw为500 MHz,内部提供了1:1/1:2降速率逻辑,其输出A、B、C、D四路的数据速率分别为fsw/2,数据宽度为8位,电平为差分LVDS,数据宽度为2×8=16位,但是,由于速率已经是250MSPS,故可以直接送给FPGA处理,而不需要再进行专门的降速率处理。

StratixII系列FPGA是Altera公司具有全新构架的高密度产品。它采用1.2V电压、90nm及全铜层SRAM工艺,是采用自适应构架的FPGA。与第一代Stratix相比,StratixII器件的逻辑密度是前者的2倍,速度也快了50%,在无线通信、高速数字信号处理和军事雷达等领域都有广泛的应用前景。本设计采用其中的EP2S90系列,该系列由三种不同大小的集成RAM块组成,包括512 bit的M512块、4 Kbit的M4K块以及512 Kbit的M-RAM块)。其中最大容量的M-RAM块就有4块,基于这三种块的RAM单元最多能达到9 Mbits的容量,因此,StratixII系列FPGA是那些对存储量要求很高的应用的理想选择。

3 系统的实现及仿真

ADC接口及控制模块

本系统选用AT84AD001B芯片,设计模拟输入的工作方式为I通道与Q通道有相互独立的两路输入,时钟输入的丁作方式为I通道和O通道有各自独立的时钟,并分别在上升沿时采样。

AT84AD001B有MODE、CLK、LDN及DATA等4个引脚用于三线串口配置。其中,MODE为高时,启用三线串口,设计时可将此引脚接入FPGA中,以便在FPGA中可以根据自身需要进行MODE的置0与置1的配置;CLK为三线串口的配置时钟输入引脚,该引脚允许输入的最大时钟频率是50 MHz,本设计的输入时钟为20 MHz,可以符合要求;LDN为通过三线串口配置寄存器的开始和结束信号的输入引脚;DATA为三线串口的寄存器配置数据输入引脚。

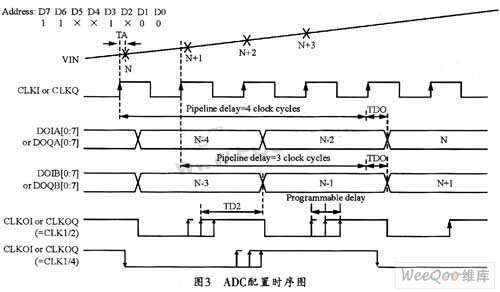

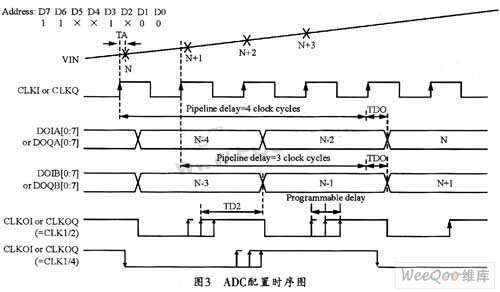

每个三线串口寄存器所需输人的配置数据包括3 bit的寄存器地址和16 bit送人该寄存器的数据,总共需配置8个寄存器,其相关时序图如3所示。

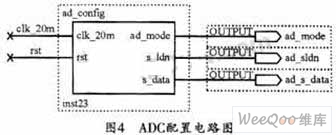

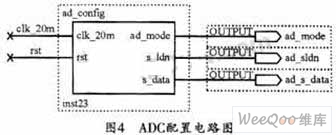

根据以上高速采样相关的三线串口组成情况,可以得到如图4所示的AD配置电路。

图4中各管脚的定义如下:

clk_20m:三线串口时钟输入;

rst:复位;

ad_mode:配置模式;

s_ldn:标志信号脚;

s_data:寄存器数据输人;

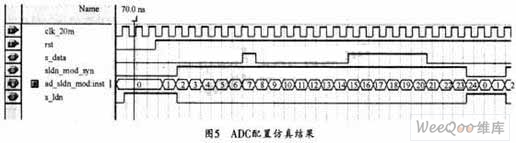

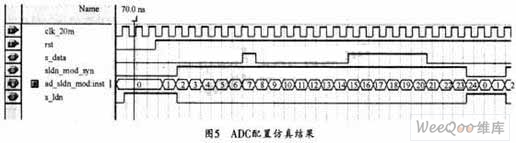

其仿真结果如图5所示,由图5可见,在ldn上升沿时寄存器数据开始输入,每20个周期读入一个寄存器数据。由此结果,即可知配置正确。

3.2 大容量FIFO数据缓存模块

由于采集的雷达信号数据量很大,所以,本系统通过Quartus中软件自带的宏功能MegaWizardPlag_in Manager来产生一个64 bit×32768words的大容量FIFO,从而有效地利用了这片FPGA的存储资源。其产生的FIFO模块如图6所示。

图6中,64位数据由ADC的高速数据采样提供,ADC的I、Q两路数据均为16位宽。为了获得更高的速度以及更大的数据缓存量,在数据进入FIFO之前,可对ADC的采样数据进行数据抽取和拼接,以将两组32位宽的IQ数据拼接成64位宽数据,然后一次送入FIFO中进行缓存。FIFO的wrreq写使能信号由前面提到的视频检测脉冲以及DSP的控制信号共同提供,其中写时钟wrclk与ADC数据拼接时钟同步,读时钟rdclk与DSP时钟同步,FIFO数据出口与DSP总线相连接。

系统的其他配置以及外围接口由于不是本文的重点,在此省略不讲。

在Ouartus平台下进行时钟分配、三线串口配置等相关处理,以及信号处理模块综合后,所得到的系统资源使用情况如图7所示。然后再利用VisualDSP++5.0平台读取采样信号数据,并用plot进行绘图,即可得到如图8所示的高速采样结果图。

4 结束语

本文是在参与实际项目的基础上完成的,本系统目前已经应用于某雷达信号处理机中。随着高速器件的开发和利用,数字接收机技术的迅速发展,其信号采集与处理的速度必将更快,处理质量会更好,处理数据量也会更大。

1 系统基本构架

本文所设计的高速数据采集系统是某雷达信号处理系统的一部分,可用于雷达信号的预处理以及采集、缓存。本系统以高速FPGA为核心逻辑控制模块,并与高速ADC和DSP相连接。其系统基本架构如图1所示。

图1中的FPGA可用作数字接收机的预处理模块,该器件集成有PPL倍频、ADC控制接口、FIFO及其管理、SPI接口、DSP总线接口、状态和自检模块等。FPGA的内部结构功能框图如图2所示。

图2中的中断产生模块用于产生周期性中断,利用视频包络和100 MHz时钟可形成50 MHz的DMA同步传送时钟,然后通过外部口DMA方式将采样数据传送到DSP。ADC控制串行接口为通用三线串口,SPI总线接口实际上是一个串并转换器,可用于控制本振。本系统的DSP数据总线为64位宽度,地址为32位。

由于雷达信号接收机中的信号处理量大,信号复杂,因此,通过基于高速大容量FPGA芯片的实时数据采集系统可以很好的满足对信号预处理的需要。

2 芯片的选取

ADC是数据采集系统的核心,其性能指标往往是决定数据采集系统性能最关键的因素。本系统的中频频率为1125 MHz,带宽BW为250 MHz。ADC选用ATMEL公司的高速采样芯片AT84AD001本系统采用带通采样方式,其采样频率低于输人中频频率。但是ADC的输入带宽必须大于中频频率加二分之一带宽,AT84AD001的模拟输入带宽为1500 MHz,高于1125+125=1250 MHz,故可满足设计要求。AT84AD001的最高采样率为1000MHz,也可以满足系统要求。此外,AT84AD001的模拟输入、时钟输入和输出全部采用差分方式。设采样时钟频率fsw为500 MHz,内部提供了1:1/1:2降速率逻辑,其输出A、B、C、D四路的数据速率分别为fsw/2,数据宽度为8位,电平为差分LVDS,数据宽度为2×8=16位,但是,由于速率已经是250MSPS,故可以直接送给FPGA处理,而不需要再进行专门的降速率处理。

StratixII系列FPGA是Altera公司具有全新构架的高密度产品。它采用1.2V电压、90nm及全铜层SRAM工艺,是采用自适应构架的FPGA。与第一代Stratix相比,StratixII器件的逻辑密度是前者的2倍,速度也快了50%,在无线通信、高速数字信号处理和军事雷达等领域都有广泛的应用前景。本设计采用其中的EP2S90系列,该系列由三种不同大小的集成RAM块组成,包括512 bit的M512块、4 Kbit的M4K块以及512 Kbit的M-RAM块)。其中最大容量的M-RAM块就有4块,基于这三种块的RAM单元最多能达到9 Mbits的容量,因此,StratixII系列FPGA是那些对存储量要求很高的应用的理想选择。

3 系统的实现及仿真

ADC接口及控制模块

本系统选用AT84AD001B芯片,设计模拟输入的工作方式为I通道与Q通道有相互独立的两路输入,时钟输入的丁作方式为I通道和O通道有各自独立的时钟,并分别在上升沿时采样。

AT84AD001B有MODE、CLK、LDN及DATA等4个引脚用于三线串口配置。其中,MODE为高时,启用三线串口,设计时可将此引脚接入FPGA中,以便在FPGA中可以根据自身需要进行MODE的置0与置1的配置;CLK为三线串口的配置时钟输入引脚,该引脚允许输入的最大时钟频率是50 MHz,本设计的输入时钟为20 MHz,可以符合要求;LDN为通过三线串口配置寄存器的开始和结束信号的输入引脚;DATA为三线串口的寄存器配置数据输入引脚。

每个三线串口寄存器所需输人的配置数据包括3 bit的寄存器地址和16 bit送人该寄存器的数据,总共需配置8个寄存器,其相关时序图如3所示。

根据以上高速采样相关的三线串口组成情况,可以得到如图4所示的AD配置电路。

图4中各管脚的定义如下:

clk_20m:三线串口时钟输入;

rst:复位;

ad_mode:配置模式;

s_ldn:标志信号脚;

s_data:寄存器数据输人;

其仿真结果如图5所示,由图5可见,在ldn上升沿时寄存器数据开始输入,每20个周期读入一个寄存器数据。由此结果,即可知配置正确。

3.2 大容量FIFO数据缓存模块

由于采集的雷达信号数据量很大,所以,本系统通过Quartus中软件自带的宏功能MegaWizardPlag_in Manager来产生一个64 bit×32768words的大容量FIFO,从而有效地利用了这片FPGA的存储资源。其产生的FIFO模块如图6所示。

图6中,64位数据由ADC的高速数据采样提供,ADC的I、Q两路数据均为16位宽。为了获得更高的速度以及更大的数据缓存量,在数据进入FIFO之前,可对ADC的采样数据进行数据抽取和拼接,以将两组32位宽的IQ数据拼接成64位宽数据,然后一次送入FIFO中进行缓存。FIFO的wrreq写使能信号由前面提到的视频检测脉冲以及DSP的控制信号共同提供,其中写时钟wrclk与ADC数据拼接时钟同步,读时钟rdclk与DSP时钟同步,FIFO数据出口与DSP总线相连接。

系统的其他配置以及外围接口由于不是本文的重点,在此省略不讲。

在Ouartus平台下进行时钟分配、三线串口配置等相关处理,以及信号处理模块综合后,所得到的系统资源使用情况如图7所示。然后再利用VisualDSP++5.0平台读取采样信号数据,并用plot进行绘图,即可得到如图8所示的高速采样结果图。

4 结束语

本文是在参与实际项目的基础上完成的,本系统目前已经应用于某雷达信号处理机中。随着高速器件的开发和利用,数字接收机技术的迅速发展,其信号采集与处理的速度必将更快,处理质量会更好,处理数据量也会更大。

FPGA 单片机 DSP 电路 EDA ADC 总线 Altera 电压 仿真 Quartus 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)