CPLD通用写入器设计与开发

时间:08-18

来源:互联网

点击:

一. CPLD及其功能

可编程逻辑器件包括现场可编程门阵列FPGA(FiLED Programmable Gate Array)和复杂可编程逻辑器件CPLD(Complex Programmable Logic Devic)这两种类型。

具有固定数目输入和输出的任何组合逻辑函数可以在可编程只读存储器PROM中以输出为输入的查找表方式来实现,许多实现组合逻辑的结构变型已从这一简单的概念引申出来,而利用VLSI的密度产生更通用的能实现PCB板上几个简单PAL互连功能的器件是PAL/PROM这类范例的扩展,称为PAL构造的PLD,即复杂可编程逻辑器件——CPLD。

CPLD所提供的逻辑资源比较少,最高约一万门。但是,CPLD提供了以下特殊功能:

1. CPLD在设计过程中为客户提供了更大的灵活性,因为对于CPLD来说,设计反复只需要改变编程文件就可以了,而且设计改变的结果可立即在工作器件中看到。CPLD不需要漫长的前置时间来制造原型或正式产品,CPLD器件已经放在分销商的货架上并可随时付运;

2. CPLD不需要客户支付高昂的NRE成本和购买昂贵的掩膜组,因为CPLD供应商在设计其可编程器件时已经支付了这些成本,并且可通过PLD产品线延续多年的生命期来分摊这些成本;

3. CPLD允许客户在需要时订购所需要的数量,从而使客户可控制库存。采用固定逻辑器件的客户经常会面临需要废弃的过量库存,而当对其产品的需求高涨时,他们有可能为器件供货不足所苦,并且不得不面对生产延迟的现实;

4. CPLD甚至在设备付运到客户那儿以后还可以重新编程。正是由于有了可编程逻辑器件,一些设备制造商现在正在尝试为已经安装在现场的产品增加新功能或者进行升级。

二. Xilinx公司的XC9500系列可编程逻辑器件

近年来,可编程逻辑器件在高密度、高速度、低功耗等方面发展很快。在CPLD方面,Xilinx公司推出了高性能、低成本的XC9500[tm]系列,以及在单个器件内结合了极低功耗和高速度、高密度和多I/O引脚特点的CoolRunner[tm]系列。此系列CPLD器件需要的功耗极低,并且价格低廉,从而使其对于成本敏感的、电池供电的便携式设备(如移动电话和数字手持助理)非常理想。

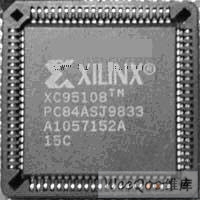

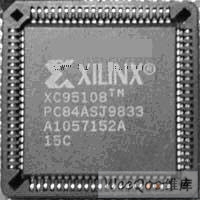

XC9500系列CPLD器件是Xilinx公司具有代表性的产品,图1为XC9500系列芯片的外观图:

图1 XC9500系列芯片的外观图

三. CPLD的设计与开发

XC9500系列可编程逻辑器件的内部结构以及时序问题就不一一介绍了,我们下面所关心的是CPLD的设计与开发。

CPLD器件的设计一般可以分为设计输入、设计实现、设计仿真和下载编程4个步骤:

1. 设计输入

设计输入就是将设计者所设计的电路以开发软件要求的某种形式表达出来,并输入到相应的软件中。

2. 设计实现

在设计输入之后,实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与I/O功能块连接的布线通道。Xilinx设计实现工具以极高自动化程度完成这些任务,设计编译实用程序自动地恢复所有的输入文件,执行所有必要的步骤来产生CPLD的配置程序。

3. 设计仿真

这一部分的最大功能是便于用户查看自己的设计思想是否得到实现。我们可以在设计的过程中对整个系统乃至各个模块进行仿真,如果有问题,可以很方便地修改错误,而不必在硬件上动手脚。仿真不消耗资源,不浪费时间,实乃可编程逻辑器件设计与开发精髓之所在。

4. 下载编程

下载编程一块是将设计阶段生成的JEDEC文件装入到可编程器件中,是本文的重点。器件编程需要满足一定的条件,如编程电压、编程时序和编程算法等。普通的CPLD器件需要一种编程专用设备(编程器)完成器件编程。

Xilinx商提供基于IEEE1149.1,JTAG协议(JTAG Boundary Scan)的CPLD编程写入器。它由DSUB

—25接口和下载电缆组成,被开发的CPLD必须在开发基板上进行编程,板上就必须留有JTAG使用的接口(TMS,TCK,TDI和TDO信号线等)。这样的好处是我们能够实机调试。

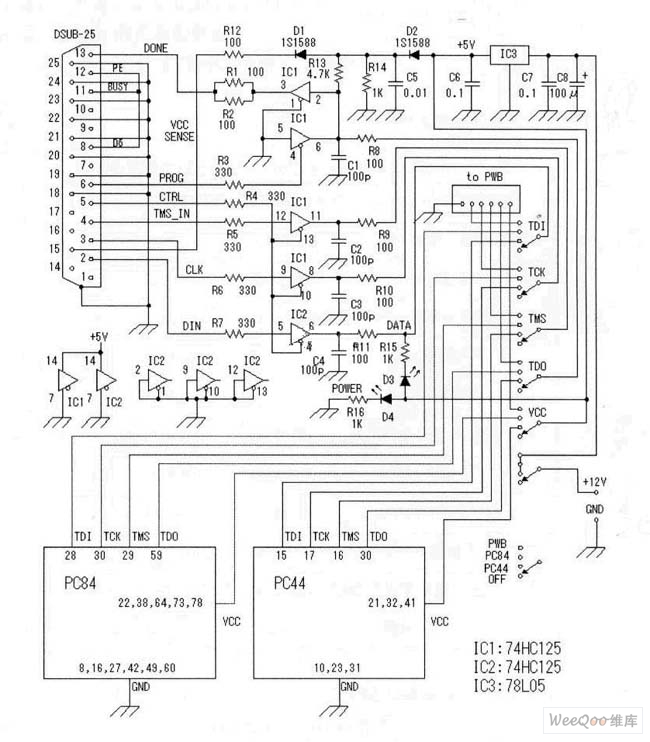

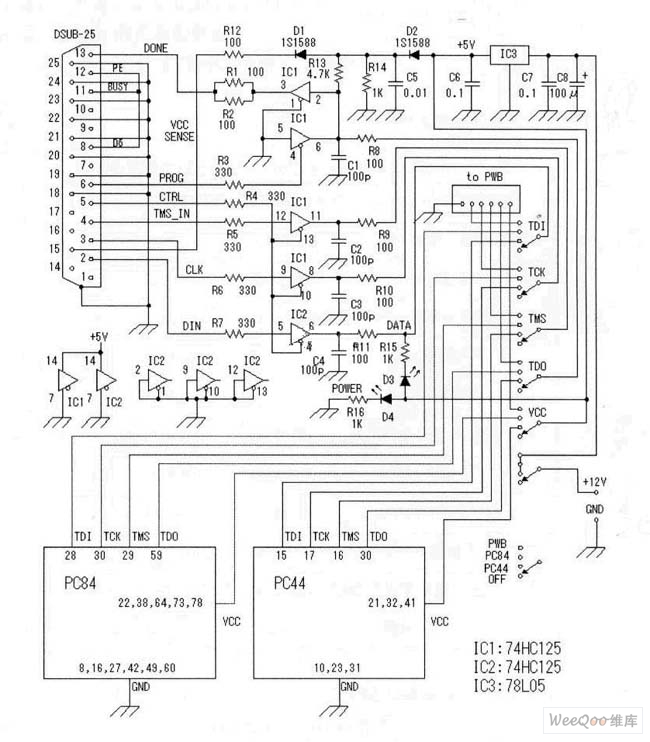

除Xilinx的实机编程器外,还可设计脱机CPLD编程写入器(电路如图2),它能对CPLD进行编程写入,而不需要开发实物基板,实物基板设计时就不需要留有JTAG接口。这样能节约基板,减少产品体积。图2的设计电路有以下几个主要的部件:

1. 并行接口

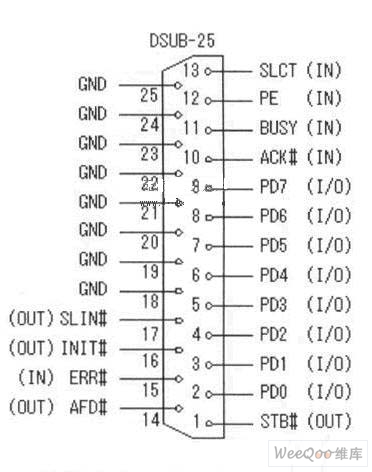

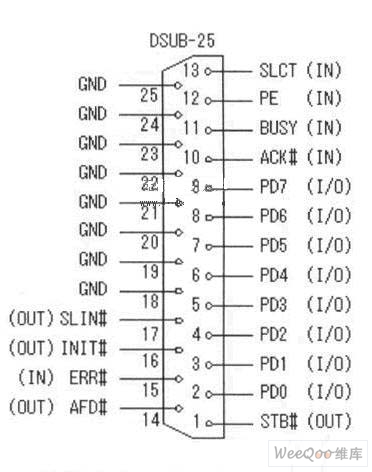

在图2中,我们可以看到一个Parallel并行接口,用它经过数据线和计算机连接。其实在这里,我们也可以使用其它接口,例如Multilinx/Serial串行接口,以及Multilinx/USB接口等。这里使用的端口也是我们经常用于连接本地打印机的接口。该接口是具有25Pin的接口,它的各Pin端口的信号如图3所示。

图2 CPLD编程写入器总电原理图

图3 Parallel并行接口图

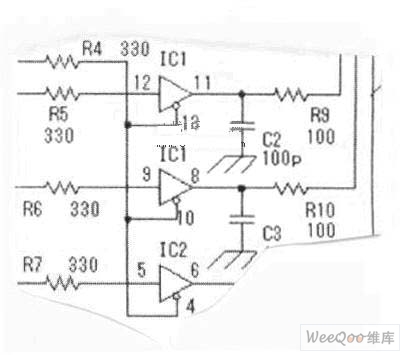

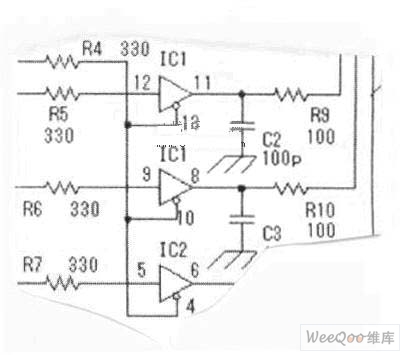

2. Bus/Buffer电路

JTAG的信号,如TMS,TCK,TDI和TDO均需要设置Bus/Buffer电路。该Buffer电路采用了三态电路,这样的设计使得CPLD写入器对计算机的并行接口无不良影响,仅在需要对CPLD写入器进行数据输入输出时才动作。在不输入输出信号数据时它处于高阻状态,在需输入输出数据时才处于低阻状态,保证对CPLD写入,读出所需电流。Bus/Buffer电路如图4所示:

图4 Bus/Buffer电路

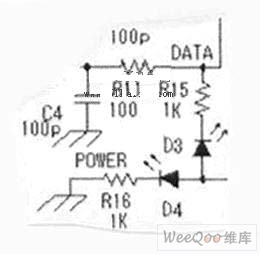

图5 LED表示电路

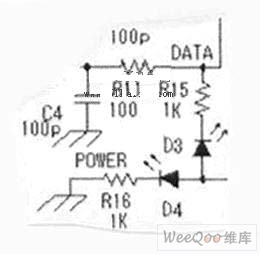

3. LED表示电路

在CPLD编程写入器电路设计中还设计有各种LED表示电路。如设置有绿色LED来表示电源输出情况,红色LED在TDI信号为L低电平时点灯。在红色LED点灭时表示传送数据中,此时不能关机或拔连接电缆。LED表示电路如图5所示。

4. Device切换电路

对不同的CPLD芯片(如PC84,PC44等)进行编程写入,它的选择由旋转切换开关来完成,由于篇幅的关系就不给出了。

本文作者创新点及其经济效益:设计出CPLD脱机编程写入器,对CPLD进行编程写入,而不需要开发实物基板,实物基板设计时就不需要留有JTAG接口。这样能节约基板,减少产品体积。

可编程逻辑器件包括现场可编程门阵列FPGA(FiLED Programmable Gate Array)和复杂可编程逻辑器件CPLD(Complex Programmable Logic Devic)这两种类型。

具有固定数目输入和输出的任何组合逻辑函数可以在可编程只读存储器PROM中以输出为输入的查找表方式来实现,许多实现组合逻辑的结构变型已从这一简单的概念引申出来,而利用VLSI的密度产生更通用的能实现PCB板上几个简单PAL互连功能的器件是PAL/PROM这类范例的扩展,称为PAL构造的PLD,即复杂可编程逻辑器件——CPLD。

CPLD所提供的逻辑资源比较少,最高约一万门。但是,CPLD提供了以下特殊功能:

1. CPLD在设计过程中为客户提供了更大的灵活性,因为对于CPLD来说,设计反复只需要改变编程文件就可以了,而且设计改变的结果可立即在工作器件中看到。CPLD不需要漫长的前置时间来制造原型或正式产品,CPLD器件已经放在分销商的货架上并可随时付运;

2. CPLD不需要客户支付高昂的NRE成本和购买昂贵的掩膜组,因为CPLD供应商在设计其可编程器件时已经支付了这些成本,并且可通过PLD产品线延续多年的生命期来分摊这些成本;

3. CPLD允许客户在需要时订购所需要的数量,从而使客户可控制库存。采用固定逻辑器件的客户经常会面临需要废弃的过量库存,而当对其产品的需求高涨时,他们有可能为器件供货不足所苦,并且不得不面对生产延迟的现实;

4. CPLD甚至在设备付运到客户那儿以后还可以重新编程。正是由于有了可编程逻辑器件,一些设备制造商现在正在尝试为已经安装在现场的产品增加新功能或者进行升级。

二. Xilinx公司的XC9500系列可编程逻辑器件

近年来,可编程逻辑器件在高密度、高速度、低功耗等方面发展很快。在CPLD方面,Xilinx公司推出了高性能、低成本的XC9500[tm]系列,以及在单个器件内结合了极低功耗和高速度、高密度和多I/O引脚特点的CoolRunner[tm]系列。此系列CPLD器件需要的功耗极低,并且价格低廉,从而使其对于成本敏感的、电池供电的便携式设备(如移动电话和数字手持助理)非常理想。

XC9500系列CPLD器件是Xilinx公司具有代表性的产品,图1为XC9500系列芯片的外观图:

图1 XC9500系列芯片的外观图

三. CPLD的设计与开发

XC9500系列可编程逻辑器件的内部结构以及时序问题就不一一介绍了,我们下面所关心的是CPLD的设计与开发。

CPLD器件的设计一般可以分为设计输入、设计实现、设计仿真和下载编程4个步骤:

1. 设计输入

设计输入就是将设计者所设计的电路以开发软件要求的某种形式表达出来,并输入到相应的软件中。

2. 设计实现

在设计输入之后,实现工具把逻辑映射到目标器件结构的资源中,决定逻辑的最佳布局,选择逻辑与I/O功能块连接的布线通道。Xilinx设计实现工具以极高自动化程度完成这些任务,设计编译实用程序自动地恢复所有的输入文件,执行所有必要的步骤来产生CPLD的配置程序。

3. 设计仿真

这一部分的最大功能是便于用户查看自己的设计思想是否得到实现。我们可以在设计的过程中对整个系统乃至各个模块进行仿真,如果有问题,可以很方便地修改错误,而不必在硬件上动手脚。仿真不消耗资源,不浪费时间,实乃可编程逻辑器件设计与开发精髓之所在。

4. 下载编程

下载编程一块是将设计阶段生成的JEDEC文件装入到可编程器件中,是本文的重点。器件编程需要满足一定的条件,如编程电压、编程时序和编程算法等。普通的CPLD器件需要一种编程专用设备(编程器)完成器件编程。

Xilinx商提供基于IEEE1149.1,JTAG协议(JTAG Boundary Scan)的CPLD编程写入器。它由DSUB

—25接口和下载电缆组成,被开发的CPLD必须在开发基板上进行编程,板上就必须留有JTAG使用的接口(TMS,TCK,TDI和TDO信号线等)。这样的好处是我们能够实机调试。

除Xilinx的实机编程器外,还可设计脱机CPLD编程写入器(电路如图2),它能对CPLD进行编程写入,而不需要开发实物基板,实物基板设计时就不需要留有JTAG接口。这样能节约基板,减少产品体积。图2的设计电路有以下几个主要的部件:

1. 并行接口

在图2中,我们可以看到一个Parallel并行接口,用它经过数据线和计算机连接。其实在这里,我们也可以使用其它接口,例如Multilinx/Serial串行接口,以及Multilinx/USB接口等。这里使用的端口也是我们经常用于连接本地打印机的接口。该接口是具有25Pin的接口,它的各Pin端口的信号如图3所示。

图2 CPLD编程写入器总电原理图

图3 Parallel并行接口图

2. Bus/Buffer电路

JTAG的信号,如TMS,TCK,TDI和TDO均需要设置Bus/Buffer电路。该Buffer电路采用了三态电路,这样的设计使得CPLD写入器对计算机的并行接口无不良影响,仅在需要对CPLD写入器进行数据输入输出时才动作。在不输入输出信号数据时它处于高阻状态,在需输入输出数据时才处于低阻状态,保证对CPLD写入,读出所需电流。Bus/Buffer电路如图4所示:

图4 Bus/Buffer电路

图5 LED表示电路

3. LED表示电路

在CPLD编程写入器电路设计中还设计有各种LED表示电路。如设置有绿色LED来表示电源输出情况,红色LED在TDI信号为L低电平时点灯。在红色LED点灭时表示传送数据中,此时不能关机或拔连接电缆。LED表示电路如图5所示。

4. Device切换电路

对不同的CPLD芯片(如PC84,PC44等)进行编程写入,它的选择由旋转切换开关来完成,由于篇幅的关系就不给出了。

本文作者创新点及其经济效益:设计出CPLD脱机编程写入器,对CPLD进行编程写入,而不需要开发实物基板,实物基板设计时就不需要留有JTAG接口。这样能节约基板,减少产品体积。

CPLD FPGA LED PCB Xilinx 仿真 电路 自动化 电压 USB 电流 相关文章:

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- Virtex-5推动超宽带通信和测距的发展(01-06)