加速FPGA系统实时调试技术

时间:07-26

来源:互联网

点击:

快速使用FPGAView

可以通过下面几个简单的步骤使用FPGAView:

第1步. 在设计中配置和插入相应的测试内核

第2步. 加载测试内核信息

第3步. 建立FPGA针脚与TLA逻辑分析仪通道的对应关系

第4步. 进行测量

下面几节详细介绍了每个步骤。

第1步. 插入内核

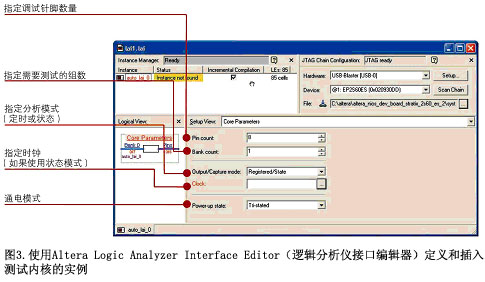

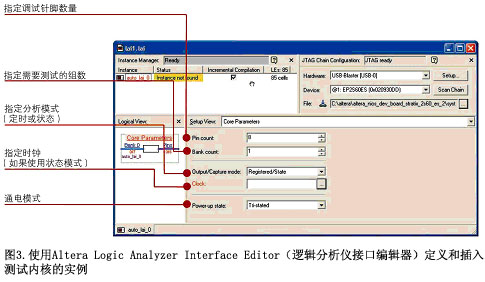

第一步是配置测试内核,把它插入到FPGA设计中。例如,在使用Altera或Xilinx器件时,可以使用FPGA开发工具提供的逻辑分析仪接口编辑器,创建最适合自己需求的测试核(参见图3)。

[图示内容:]

Specify number of debug pins: 指定调试针脚数量

Specify Number of Banks: 指定需要测试的组数

Specify Mode: 指定分析模式(定时或状态)

Specify Clock (if using State Mode): 指定时钟(如果使用状态模式)

Power-Up Mode: 通电模式

对大多数测试内核,可以指定下述参数:

Pin Count(针脚数量) :表示希望专用于逻辑分析仪接口的针脚数量。

Bank Count(组数) :表示希望映射到每个针脚上的内部信号数量。

Output/Capture Mode(输出/捕获模式):选择希望执行的采集类型。可以选择Combination/Timing(组合逻辑/定时模式) 或Registered/State (寄存器/状态模式)。

Clock(时钟) :如果用户选择了Registered/State(寄存器/状态)的捕获模式,这一选项允许选择测试内核的取样时钟。

Power-Up State(通电状态) :这个参数允许指明指定用于逻辑分析仪接口的针脚的通电状态。

第2步. 把测试内核信息加载到FPGAView中

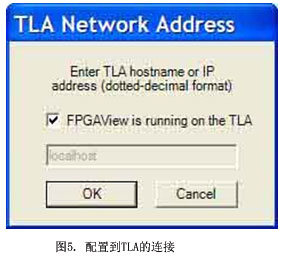

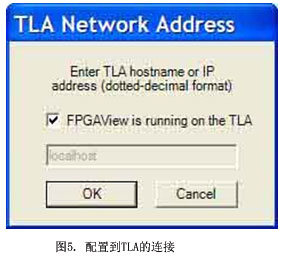

从FPGAView软件窗口中,可以与JTAG编程电缆建立连接(参见图4),并且连接到TLA系列逻辑分析仪(TLA逻辑分析仪使用WINDOWS平台)或PC工作站上(参见图5)。

在使用ALTERA FPGA芯片时,按Open (打开)工具条按钮,调出一个文件浏览器,选择Quartus II LAI Editor软件以前生成的逻辑分析仪接口(.lai)文件。这样就加载了与LAI核心有关的所有信息,包括每一组的信号数量、组数和信号名称,另外如果设备中的LAI内核多于一个,那么还包括每个LAI内核的信息。

第3步.

把FPGA针脚映射到逻辑分析仪上

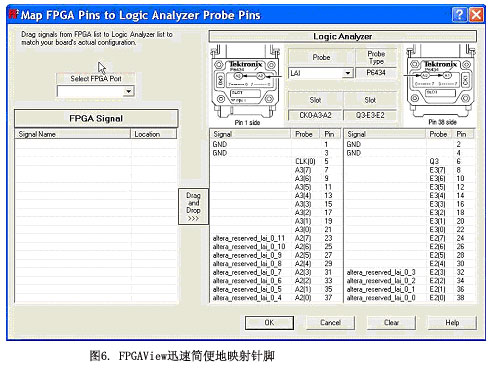

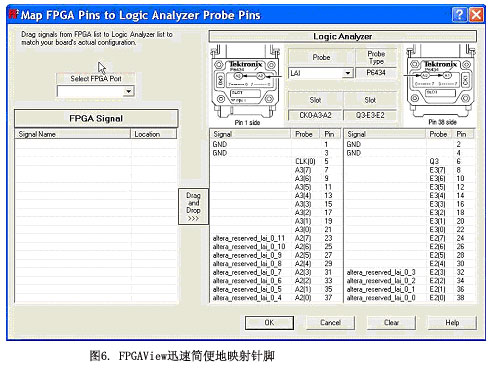

下一步是映射FPGA针脚和TLA逻辑分析仪探头之间的物理连接。FPGAView可以自动更新逻辑分析仪上显示的信号名称,与测试内核当前监测的信号相匹配。

为此,简单地点击Probes (探头)按钮,将出现一个拖放窗口,把测试内核输出信号名称与逻辑分析仪上的相应通道连接起来(参见图6)。。对某条目标连接,这个通道分配过程只需一次。

第4步. 进行测量

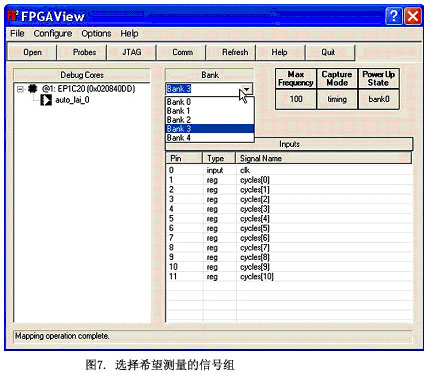

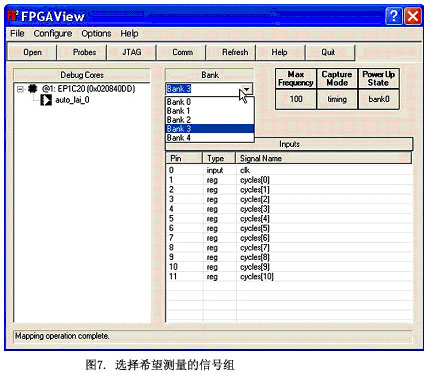

使用Bank(组)列表下拉菜单,选择想要测量的组。一旦选择了组,FPGAView会通过JTAG接口与FPGA通信,并配置测试内核,以便选择希望的组。

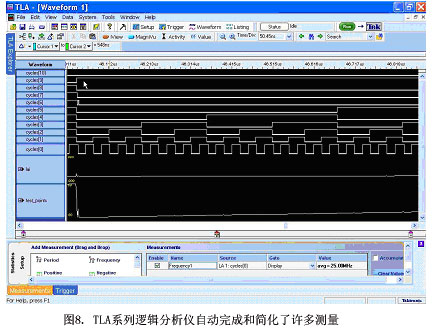

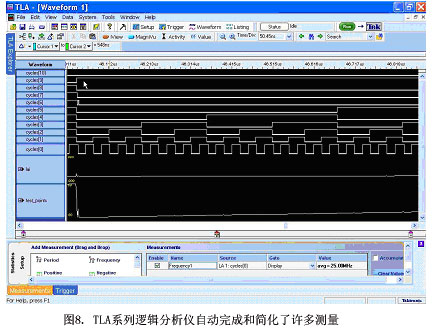

FPGAView还将这些通道名称通过对TLA系列逻辑分析仪的控制进行自动分配,从而可以简便地理解测量结果。为测量不同的一套内部信号,用户只需选择不同的信号组(参见图7)。全功能TLA系列逻辑分析仪会自动把这些FPGA信号与系统中的其它信号关联起来(参见图8)。

在TLA逻辑分析仪中,针对设计人员关心的各种时间信息,提供了业内独有的定时参数自动测量功能,通过鼠标简单的拖放操作,能够得到周期、频率、占空比、脉冲宽度、通道/通道延迟、边沿计数、周期计数、违规计数、周期抖动、以及周期间抖动等信息。

小结

通过在FPGA系统和设计与应用阶段认真考虑调试需求,可以选择相应的调试方法,既简化调试流程,也有助于节约时间。嵌入式逻辑分析仪和外部逻辑分析仪这两种方法各有优缺点,但FPGAView等新方法进一步提高了外部逻辑分析仪方法的吸引力。能够快速方便地移动探点,而不需重新汇编设计,同时能够把内部FPGA信号活动与电路板级信号关联起来,直接决定着能否满足产品开发周期的要求。

可以通过下面几个简单的步骤使用FPGAView:

第1步. 在设计中配置和插入相应的测试内核

第2步. 加载测试内核信息

第3步. 建立FPGA针脚与TLA逻辑分析仪通道的对应关系

第4步. 进行测量

下面几节详细介绍了每个步骤。

第1步. 插入内核

第一步是配置测试内核,把它插入到FPGA设计中。例如,在使用Altera或Xilinx器件时,可以使用FPGA开发工具提供的逻辑分析仪接口编辑器,创建最适合自己需求的测试核(参见图3)。

[图示内容:]

Specify number of debug pins: 指定调试针脚数量

Specify Number of Banks: 指定需要测试的组数

Specify Mode: 指定分析模式(定时或状态)

Specify Clock (if using State Mode): 指定时钟(如果使用状态模式)

Power-Up Mode: 通电模式

对大多数测试内核,可以指定下述参数:

Pin Count(针脚数量) :表示希望专用于逻辑分析仪接口的针脚数量。

Bank Count(组数) :表示希望映射到每个针脚上的内部信号数量。

Output/Capture Mode(输出/捕获模式):选择希望执行的采集类型。可以选择Combination/Timing(组合逻辑/定时模式) 或Registered/State (寄存器/状态模式)。

Clock(时钟) :如果用户选择了Registered/State(寄存器/状态)的捕获模式,这一选项允许选择测试内核的取样时钟。

Power-Up State(通电状态) :这个参数允许指明指定用于逻辑分析仪接口的针脚的通电状态。

第2步. 把测试内核信息加载到FPGAView中

从FPGAView软件窗口中,可以与JTAG编程电缆建立连接(参见图4),并且连接到TLA系列逻辑分析仪(TLA逻辑分析仪使用WINDOWS平台)或PC工作站上(参见图5)。

在使用ALTERA FPGA芯片时,按Open (打开)工具条按钮,调出一个文件浏览器,选择Quartus II LAI Editor软件以前生成的逻辑分析仪接口(.lai)文件。这样就加载了与LAI核心有关的所有信息,包括每一组的信号数量、组数和信号名称,另外如果设备中的LAI内核多于一个,那么还包括每个LAI内核的信息。

第3步.

把FPGA针脚映射到逻辑分析仪上

下一步是映射FPGA针脚和TLA逻辑分析仪探头之间的物理连接。FPGAView可以自动更新逻辑分析仪上显示的信号名称,与测试内核当前监测的信号相匹配。

为此,简单地点击Probes (探头)按钮,将出现一个拖放窗口,把测试内核输出信号名称与逻辑分析仪上的相应通道连接起来(参见图6)。。对某条目标连接,这个通道分配过程只需一次。

第4步. 进行测量

使用Bank(组)列表下拉菜单,选择想要测量的组。一旦选择了组,FPGAView会通过JTAG接口与FPGA通信,并配置测试内核,以便选择希望的组。

FPGAView还将这些通道名称通过对TLA系列逻辑分析仪的控制进行自动分配,从而可以简便地理解测量结果。为测量不同的一套内部信号,用户只需选择不同的信号组(参见图7)。全功能TLA系列逻辑分析仪会自动把这些FPGA信号与系统中的其它信号关联起来(参见图8)。

在TLA逻辑分析仪中,针对设计人员关心的各种时间信息,提供了业内独有的定时参数自动测量功能,通过鼠标简单的拖放操作,能够得到周期、频率、占空比、脉冲宽度、通道/通道延迟、边沿计数、周期计数、违规计数、周期抖动、以及周期间抖动等信息。

小结

通过在FPGA系统和设计与应用阶段认真考虑调试需求,可以选择相应的调试方法,既简化调试流程,也有助于节约时间。嵌入式逻辑分析仪和外部逻辑分析仪这两种方法各有优缺点,但FPGAView等新方法进一步提高了外部逻辑分析仪方法的吸引力。能够快速方便地移动探点,而不需重新汇编设计,同时能够把内部FPGA信号活动与电路板级信号关联起来,直接决定着能否满足产品开发周期的要求。

FPGA 电路 PCB DSP 总线 Altera Xilinx 仿真 嵌入式 LTE 泰克 连接器 USB Quartus 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)