基于FPGA的UPFC控制器IP设计

时间:07-18

来源:互联网

点击:

2.4 正弦波幅值计算模块

由于定制的正弦数据存储器ROM的最大数据是1023,即只占用了10位数据宽度,还有6位数据宽度用于调节正弦波形的幅值。正弦波形的幅值最大调节量是其选择波形的64倍。实际上,输出正弦波形的数据等于查找到的正弦信号数据与幅值寄存器的乘积。虽然Verilog语言提供了乘法功能,但是它在有的综合器中是不能被综合的,所以必须自己设计一个乘法器。该乘法器同样可以利用MegaWizard Plug-In Manage工具提供的LPM_MULT来定制一个16×16的乘法器。

3 系统验证

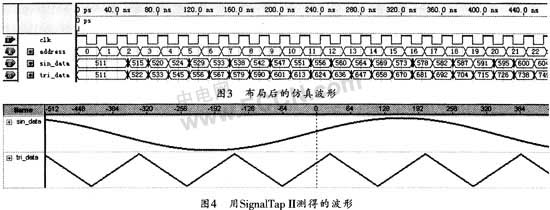

使用Quartus5.1对UPFC控制器IP核的Verilog程序进行综合时,可选用Altera公司的CycloneIIEP2C35评估板。该板有33216个逻辑单元,105个M4k存储模块,35个18×18乘法单元,4个PLL和475个I/O脚。UPFC控制器IP核在Quartus 中编译通过,即可利用波形编辑器对其进行功能仿真。图3是其功能仿真波形。实际上,Quartus提供有嵌入式逻辑分析仪SignalTap II,可以对输出信号进行实时测试。在实际监测中,通过SignalTap II可将测得的样本信号暂存于目标器件的嵌入式RAM中,然后通过器件的JTAG端口和USB Blaster下载线将采得的信息传出,并送入主机进行分析。图4为UPFC控制器IP核输出的实际波形图。

4 结束语

本UPFC控制器IP能使输出正弦波频率跟电网频率保持一致,且输出正弦波的幅值和相位可根据需要进行调节;输出的三角载波的频率、幅值和相位保持不变。同时,将UPFC控制器IP核和Nios II相结合还可提高系统的抗干扰能力。

由于定制的正弦数据存储器ROM的最大数据是1023,即只占用了10位数据宽度,还有6位数据宽度用于调节正弦波形的幅值。正弦波形的幅值最大调节量是其选择波形的64倍。实际上,输出正弦波形的数据等于查找到的正弦信号数据与幅值寄存器的乘积。虽然Verilog语言提供了乘法功能,但是它在有的综合器中是不能被综合的,所以必须自己设计一个乘法器。该乘法器同样可以利用MegaWizard Plug-In Manage工具提供的LPM_MULT来定制一个16×16的乘法器。

3 系统验证

使用Quartus5.1对UPFC控制器IP核的Verilog程序进行综合时,可选用Altera公司的CycloneIIEP2C35评估板。该板有33216个逻辑单元,105个M4k存储模块,35个18×18乘法单元,4个PLL和475个I/O脚。UPFC控制器IP核在Quartus 中编译通过,即可利用波形编辑器对其进行功能仿真。图3是其功能仿真波形。实际上,Quartus提供有嵌入式逻辑分析仪SignalTap II,可以对输出信号进行实时测试。在实际监测中,通过SignalTap II可将测得的样本信号暂存于目标器件的嵌入式RAM中,然后通过器件的JTAG端口和USB Blaster下载线将采得的信息传出,并送入主机进行分析。图4为UPFC控制器IP核输出的实际波形图。

4 结束语

本UPFC控制器IP能使输出正弦波频率跟电网频率保持一致,且输出正弦波的幅值和相位可根据需要进行调节;输出的三角载波的频率、幅值和相位保持不变。同时,将UPFC控制器IP核和Nios II相结合还可提高系统的抗干扰能力。

电流 电子 FPGA Altera Quartus 总线 PWM 信号发生器 Verilog 仿真 嵌入式 USB 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- FPGA 上同步开关噪声的分析(04-05)

- 经I/O优化的FPGA(04-23)

- 基于Actel FPGA的PWM IP的应用(09-17)

- 适用于消费性市场的nano FPGA技术(09-27)

- Altera FPGA下载配置(11-11)