基于FPGA的IDE硬盘接口卡的实现

时间:07-18

来源:互联网

点击:

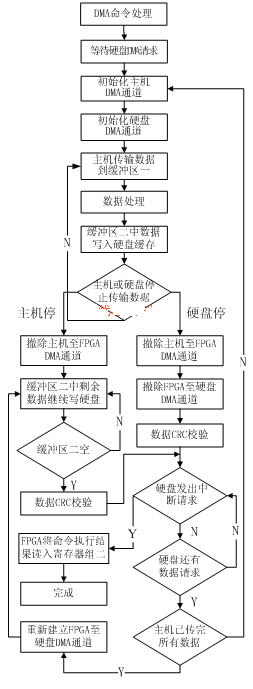

3.2 Ultra DMA命令处理流程

DMA传输通道的建立都是由硬盘通过DMARQ来请求的。FPGA接收到硬盘的DMA请求后首先初始化主机至FPGA的DMA通道,紧接着初始化FPGA至硬盘的DMA通道。此时主机经FPGA到硬盘的DMA通道即已建立,主机向缓冲区一写入数据,同时数据处理单元对数据进行加密运算,并将加密后的数据写入缓冲区二,FPGA则将缓冲区二中的数据写入硬盘。在传输过程中,若硬盘要求暂停或者缓冲区二空,则FPGA暂停向硬盘发送数据;若缓冲区一满,则FPGA要求主机暂停发送数据。

主机和硬盘都可以随时停止当前的DMA传输,未传完的数据将等待硬盘下一次的DMA请求时再进行传输。如果硬盘提出中止传输,FPGA将撤除FPGA至硬盘的DMA通道,同时向主机提出中止传输,撤除主机至FPGA的DMA通道,并计算该次所传数据的CRC校验。然后FPGA进入等待状态,等待硬盘下一次的DMA请求。

如果主机提出中止传输,FPGA将撤除主机至FPGA的DMA通道,同时继续向硬盘发送数据,直到将接收到主机的数据发送完毕,即缓冲区二空后,向硬盘提出中止传输,撤除FPGA至硬盘的DMA通道,并计算CRC校验。然后FPGA进入等待状态,等待硬盘下一次的DMA请求。

在等待状态下,若FPGA接收到硬盘的中断请求,则说明该次命令的所有数据已经传完,命令结束。FPGA将命令执行结果读入寄存器组二,向主机产生中断请求,进入空闲状态。若接收到硬盘的DMA请求,则说明硬盘还未接收到该次命令的所有数据,此时需要判断主机是否已将所有数据发送完。如果主机并没有将所有数据发送完,则再次建立FPGA两侧的DMA通道,开始新一轮的DMA传输;如果主机已将所有数据发送完,则重新建立FPGA至硬盘的DMA通道,直到将缓冲区二中的数据发送完,并计算CRC校验。

4 结束语

本文采用FPGA实现了两套符合ATA-6规范的IDE接口,完成主机与硬盘之间数据的截获、处理和转发。经测试,系统在DOS、Windows 98、Windows? 2000、Windows XP及 Red Hat Linux 9.0操作系统环境下,使用希捷、迈拓、三星、西数等公司的多种型号硬盘均工作正常,支持PIO和Ultra DMA两种数据传输模式。由于通过FPGA实现一个完整的IDE接口,若对系统稍加改动,如在数据处理单元中加入相应的文件系统,即可实现脱机读写IDE硬盘,用于数据采集的海量存储等多种场合,使系统具有较好的通用性。

本文作者创新点:作者针对硬盘数据易泄密及高速大容量数据采集困难等问题,提出在主机和硬盘之间使用FPGA芯片构建一个双向IDE硬盘通道,实现两套符合ATA-6规范的IDE接口,FPGA对主机与硬盘间的数据流进行处理及转发,以实现硬盘数据加密、数据高速采集存储及脱机控制硬盘等操作。系统支持PIO和Ultra DMA两种数据传输模式,对操作系统透明,较常见的单向IDE通道,该系统通用性强,有较好的推广价值。本文侧重于用FPGA实现IDE接口协议,对实现过程及方法做了详细描述,对读者有较高的参考实用价值。

以Ultra DMA模式传输数据的命令有Write DMA和Read DMA。下面我们以Ultra DMA写操作为例介绍Ultra DMA命令处理流程。

DMA传输通道的建立都是由硬盘通过DMARQ来请求的。FPGA接收到硬盘的DMA请求后首先初始化主机至FPGA的DMA通道,紧接着初始化FPGA至硬盘的DMA通道。此时主机经FPGA到硬盘的DMA通道即已建立,主机向缓冲区一写入数据,同时数据处理单元对数据进行加密运算,并将加密后的数据写入缓冲区二,FPGA则将缓冲区二中的数据写入硬盘。在传输过程中,若硬盘要求暂停或者缓冲区二空,则FPGA暂停向硬盘发送数据;若缓冲区一满,则FPGA要求主机暂停发送数据。

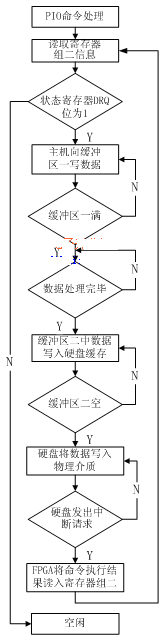

图3 PIO命令处理流程

主机和硬盘都可以随时停止当前的DMA传输,未传完的数据将等待硬盘下一次的DMA请求时再进行传输。如果硬盘提出中止传输,FPGA将撤除FPGA至硬盘的DMA通道,同时向主机提出中止传输,撤除主机至FPGA的DMA通道,并计算该次所传数据的CRC校验。然后FPGA进入等待状态,等待硬盘下一次的DMA请求。

如果主机提出中止传输,FPGA将撤除主机至FPGA的DMA通道,同时继续向硬盘发送数据,直到将接收到主机的数据发送完毕,即缓冲区二空后,向硬盘提出中止传输,撤除FPGA至硬盘的DMA通道,并计算CRC校验。然后FPGA进入等待状态,等待硬盘下一次的DMA请求。

在等待状态下,若FPGA接收到硬盘的中断请求,则说明该次命令的所有数据已经传完,命令结束。FPGA将命令执行结果读入寄存器组二,向主机产生中断请求,进入空闲状态。若接收到硬盘的DMA请求,则说明硬盘还未接收到该次命令的所有数据,此时需要判断主机是否已将所有数据发送完。如果主机并没有将所有数据发送完,则再次建立FPGA两侧的DMA通道,开始新一轮的DMA传输;如果主机已将所有数据发送完,则重新建立FPGA至硬盘的DMA通道,直到将缓冲区二中的数据发送完,并计算CRC校验。

4 结束语

本文采用FPGA实现了两套符合ATA-6规范的IDE接口,完成主机与硬盘之间数据的截获、处理和转发。经测试,系统在DOS、Windows 98、Windows? 2000、Windows XP及 Red Hat Linux 9.0操作系统环境下,使用希捷、迈拓、三星、西数等公司的多种型号硬盘均工作正常,支持PIO和Ultra DMA两种数据传输模式。由于通过FPGA实现一个完整的IDE接口,若对系统稍加改动,如在数据处理单元中加入相应的文件系统,即可实现脱机读写IDE硬盘,用于数据采集的海量存储等多种场合,使系统具有较好的通用性。

本文作者创新点:作者针对硬盘数据易泄密及高速大容量数据采集困难等问题,提出在主机和硬盘之间使用FPGA芯片构建一个双向IDE硬盘通道,实现两套符合ATA-6规范的IDE接口,FPGA对主机与硬盘间的数据流进行处理及转发,以实现硬盘数据加密、数据高速采集存储及脱机控制硬盘等操作。系统支持PIO和Ultra DMA两种数据传输模式,对操作系统透明,较常见的单向IDE通道,该系统通用性强,有较好的推广价值。本文侧重于用FPGA实现IDE接口协议,对实现过程及方法做了详细描述,对读者有较高的参考实用价值。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)