MATLAB 算法面向 FPGA 的浮点定点转换

时间:07-15

来源:互联网

点击:

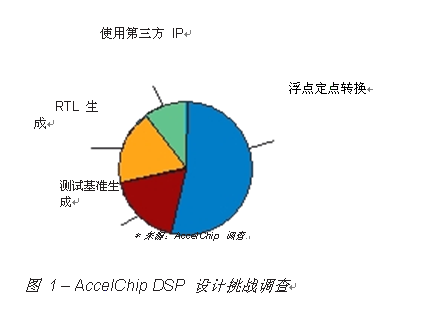

AccelChip 公司(最近已被赛灵思公司收购)最近所做的一次调查显示,53% 的回答者认为浮点定点转换是在 FPGA 上实现算法时最困难的地方(图 1)。

生成定点模型

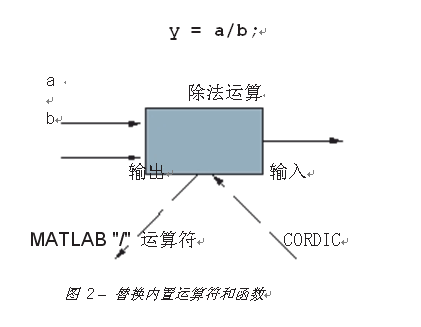

如果未将高级函数和运算符替换为硬件精确的宏架构,浮点 MATLAB 算法的定点表示将不会真正反映最终硬件的响应(图 2)。

根据数据数值,计算输出之间将存在巨大分歧。

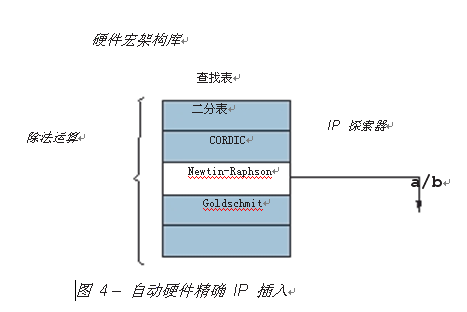

在定点生成过程中,AccelDSP™ Synthesis 综合工具的 IP Explorer™ 技术将自动使用硬件精确的表达式替换高级 MATLAB 函数和运算符(图 4)。此步骤是透明的,且不需要对 MATLAB 代码进行修改。您可以使用综合指示来重新定义初始宏架构和微架构选择。

图形辅助式自动量化

与定点 DSP 处理器不同, FPGA 结构允许使用可变定点字长。通过解除对变量的固定 16 位或 24 位边界限制,您可以执行需要位数增长的算术计算而不会引起额外的数值误差。

这对于像雷达、导航和制导系统等要求较高数值精度的应用来说是一个巨大的优点。

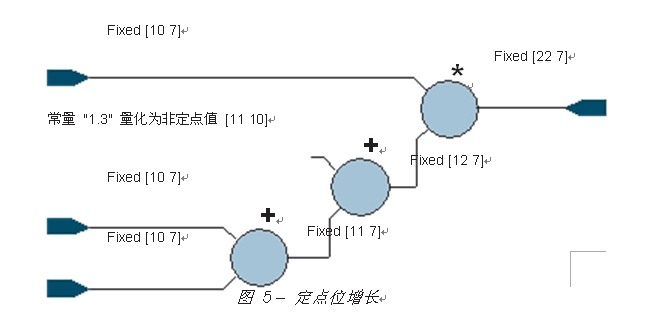

在大多数情况下,位增长率定律 (bit growth rules) 是简单直接和易于理解的。例如,一次加法的结果增长一位,而一次乘法的结果则增长到等于输入字长度的总长度(图 5)。然而,要在实际设计中确定变量的这些属性,将是一个高度反复的过程。允许未检查的位数增长现象发生,在硬件中代价是昂贵的,通常也是不必要的。如果您技术功底深厚,您可以采用各种技巧来尽可能地减小字长而同时保持数值精度。

通过自动量化而获得的初始定点模型提供了一个良好的起点,但一般需要对该模型进行细化改进。

MATLAB 提供了一种开发算法数学模型的高效环境,这种算法通常只需使用一组较少的仿真矢量就可完成。

该过程高度反复,且紧密耦合至数据作用 (data effect) 的分析。为了最大程度地缩短这一反复循环时间,AccelDSP Synthesis 综合工具提供了一种加速定点仿真流程。

分析定点数据作用

MATLAB 提供了一种开发算法数学模型的高效环境,这种算法通常只需使用一组较少的仿真矢量就可完成。但是,当把该算法应用到定点硬件时,您将需要增加数据集,以精确地确定真实世界的环境响应。MATLAB 是一种解释型仿真器,可能无法为这些较大的、CPU 强度较高的定点仿真提供必需的性能。因此,开发者常常转向 C/C++。

加速定点仿真

AccelDSP Synthesis 综合工具的 M2C-Accelerator 自动生成一个硬件精确的定点 C++ 模型和测试基准,以加快定点仿真。

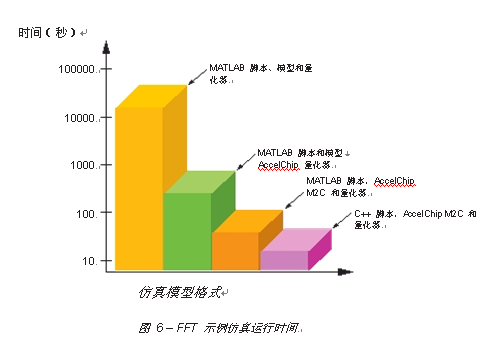

消除手动记录步骤节省了开发时间,大程度地减小了误差的引入。由于 C++ 是编译式的,因此可提供高达 1000 倍的仿真性能优势(图 6)。这种性能水平通常是那些要求理解定点数据作用的大型矢量集所必需的。

观测定点位增长

一个设计必须从整体上考虑,以有效地将浮点算法转换为定点模型。

如果从早期开始就一直未对数据路径进行检查,位增长可能会快速增长而产生过度的硬件,而过度约束位增长则可能造成无法接受的数值精度损失。获得对位增长进展情况较好观测性的一种通用技巧是向一个电子表格中输入变量。AccelDSP Synthesis 综合工具通过生成一个表格化、格式化的定点报告(图 7)而提供了此类级别的观测性。

生成定点模型

如果未将高级函数和运算符替换为硬件精确的宏架构,浮点 MATLAB 算法的定点表示将不会真正反映最终硬件的响应(图 2)。

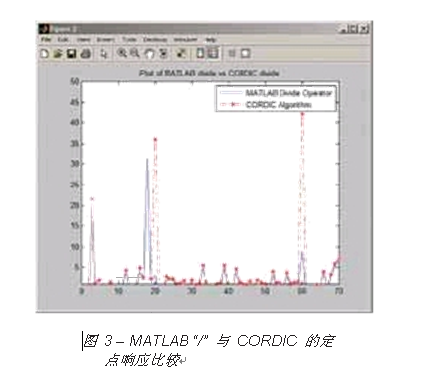

图 3 对此进行了突出显示,该图使用一组量化为 8 位有符号二进制补码的随机输入矢量,对 MATLAB 除法运算符与工具硬件 CORDIC 除法算法的定点响应进行了比较。

根据数据数值,计算输出之间将存在巨大分歧。

在定点生成过程中,AccelDSP™ Synthesis 综合工具的 IP Explorer™ 技术将自动使用硬件精确的表达式替换高级 MATLAB 函数和运算符(图 4)。此步骤是透明的,且不需要对 MATLAB 代码进行修改。您可以使用综合指示来重新定义初始宏架构和微架构选择。

图形辅助式自动量化

与定点 DSP 处理器不同, FPGA 结构允许使用可变定点字长。通过解除对变量的固定 16 位或 24 位边界限制,您可以执行需要位数增长的算术计算而不会引起额外的数值误差。

这对于像雷达、导航和制导系统等要求较高数值精度的应用来说是一个巨大的优点。

在大多数情况下,位增长率定律 (bit growth rules) 是简单直接和易于理解的。例如,一次加法的结果增长一位,而一次乘法的结果则增长到等于输入字长度的总长度(图 5)。然而,要在实际设计中确定变量的这些属性,将是一个高度反复的过程。允许未检查的位数增长现象发生,在硬件中代价是昂贵的,通常也是不必要的。如果您技术功底深厚,您可以采用各种技巧来尽可能地减小字长而同时保持数值精度。

通过自动量化而获得的初始定点模型提供了一个良好的起点,但一般需要对该模型进行细化改进。

MATLAB 提供了一种开发算法数学模型的高效环境,这种算法通常只需使用一组较少的仿真矢量就可完成。

该过程高度反复,且紧密耦合至数据作用 (data effect) 的分析。为了最大程度地缩短这一反复循环时间,AccelDSP Synthesis 综合工具提供了一种加速定点仿真流程。

分析定点数据作用

MATLAB 提供了一种开发算法数学模型的高效环境,这种算法通常只需使用一组较少的仿真矢量就可完成。但是,当把该算法应用到定点硬件时,您将需要增加数据集,以精确地确定真实世界的环境响应。MATLAB 是一种解释型仿真器,可能无法为这些较大的、CPU 强度较高的定点仿真提供必需的性能。因此,开发者常常转向 C/C++。

加速定点仿真

AccelDSP Synthesis 综合工具的 M2C-Accelerator 自动生成一个硬件精确的定点 C++ 模型和测试基准,以加快定点仿真。

消除手动记录步骤节省了开发时间,大程度地减小了误差的引入。由于 C++ 是编译式的,因此可提供高达 1000 倍的仿真性能优势(图 6)。这种性能水平通常是那些要求理解定点数据作用的大型矢量集所必需的。

观测定点位增长

一个设计必须从整体上考虑,以有效地将浮点算法转换为定点模型。

如果从早期开始就一直未对数据路径进行检查,位增长可能会快速增长而产生过度的硬件,而过度约束位增长则可能造成无法接受的数值精度损失。获得对位增长进展情况较好观测性的一种通用技巧是向一个电子表格中输入变量。AccelDSP Synthesis 综合工具通过生成一个表格化、格式化的定点报告(图 7)而提供了此类级别的观测性。

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA可帮助搜索引擎降低功耗和碳排放(09-12)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 赛灵思新版视频入门套件加快视频开发速度(05-29)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)