FPGA在数字式频分多路副载波解调器中的应用

时间:06-23

来源:互联网

点击:

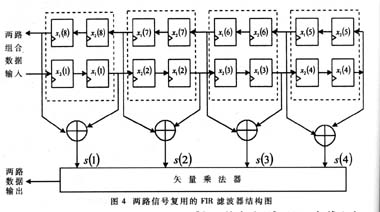

该滤波器只是在8阶FIR滤波器的基础上增加了8个移位寄存器?3,正是这8个移位寄存器使得矢量乘法器计算第一路信号时,第二路信号得以缓存;而在下一时刻到来时,才将第二路信号输出给矢量乘法器。这样就完成了两路信号的同时滤波。滤波后的信号仍以交织的形式输出,可利用分路器将它们分开。

同理,如果同时进行k路滤波,则滤波器中移位寄存器的个数将是单路FIR滤波器中移位寄存器个数的k倍。即假定FIR滤波器的阶数为N,则单路滤波器需要移位寄存器的个数为N,k路滤波器需要的移位寄存器个数为k·N。 另外,值得注意的是:采用时分复用方法后,整个系统就工作于不同的时钟频率下。假定系统采样频率为fs,进行时分复用后同时处理k路信号,则非时分复用部分的时钟频率为fs,时分复用部分的时钟频率为k·fs为使系统能够正常工作,还要在系统中加上时钟和控制电路,以控制系统的时钟和同步。图5给出了分路滤波器的时分复用框图。

利用MAX+plusII对两路信号复用滤波器的AHDL源代码进行编译,发现两路信号复用滤波器比单路滤波器多用的硬件资源不到单路硬件资源的20%。所以说,利用时分复用的方法达到了预期目标。

这种基于FPGA的数字式解调器的优点是容易和计算机相结合形成数字式FM-FM遥测数据处理系统。一方面,遥测数据可以传送给计算机,进行存储、分析和显示;另一方面,计算机也可以给数字式解调器加载不同的程序,以改变解调器的参数设置,使之适合于IRIG的全部标准。

但是,该数字式解调器仍有其不足之处,即运算精度不够高,因为利用FPGA难以进行浮点运算。如果滤波器用FPGA实现,数据宽度取12bit,鉴频器用DSP实现,采用浮点运算,则系统精度必会得到改善,但付出的代价是系统复杂度增加。

集成电路 电路 FPGA 模拟前端 滤波器 低通滤波器 DSP Maxim Altera 仿真 相关文章:

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)