验证FPGA设计:模拟,仿真,还是碰运气?

时间:08-04

来源:互联网

点击:

对ASIC开发组的观察

因此,简言之,每种方法都有优缺点。根据这些信息,有经验的ASIC设计组(即经常在其验证流程中采用FPGA者)是如何在模拟测试和基于FPGA的测试间做出平衡的呢?

视频处理器厂商Ambarella有一个例子来回答这个问题。执行副总裁Didier LeGall 说,“多数情况下,我们根本就不使用FPGA 仿真。根据我们的经验,必须得有非常成熟的RTL仿真才会有用。但是,目前流程阶段,将设计输入 FPGA和建立测试平台(的过程)是一件事倍功半的事。”

但是,实际应用情况可能会使LeGall 的看法有所调整。Ambarella 公司的SOC (片上系统) 用于以高帧速率处理高清视频和10M像素静止图像,需要采用非常快的内部时钟和复杂的算法。但是,LeGall 在对FPGA 仿真做出评论后,又对整个验证过程的目标提出了一个非常有趣的看法。“新推出IC成功的关键不在于完美的验证工作,” LeGal说。“而在于软件”:也就是说,要知道设计中哪部分比较容易出问题,并且在开始,而不是事后,就做好软件解决计划。这种策略下,验证工程师经过广泛的基于FPGA的测试所获得的很多信息的确会变得比较没用。

LSI Corp的存储元件部门提出了另一个观点。该部门的副总裁和总经理Bill Wuertz叙述了他们是如何做SCSI (小型计算机系统接口)和SAS (串行连接)控制器的。

Wuertz 说LSI采用了几乎是并行的过程,一个验证小组进行模拟实现一些目的,而另一组则采用FPGA实现另外一些目的。“在设计早期,我们建立一个称为试验 RTL(trial RTL)的步骤,” Wuertz 说。“我们要知道RTL基本工作正常、各个块互相已连接好,这是第一个点。在此阶段,验证工作分为两个方向。模拟小组编写他们的工具所用的设计,并继续对单个的块进行模拟。另一个组,即系统工程组,则通过综合RTL得到内部开发FPGA 版——我们现在正在设计第五代板卡——然后开始在系统级进行彻底的压力测试。”

如Wuertz所述,这两个组具有不同的工作目的。模拟组要努力确保电路正确。系统组通常不考虑电路,但要确保芯片在变化异常大和非常复杂的存储网络环境下可以工作。Wuertz 说FPGA 原型会与一屋子的磁盘和磁带驱动器相连运行几天的测试。“这些测试已经过了20多年的发展,”他说。“我们知道,可能需要对不同磁盘驱动器组合进行很长时间的测试后才可以产生暴露设计问题的时间匹配异常情况。”

LSI 已开发了自有的将两种环境联系起来的内部工具。例如,通过这些工具,系统组可以捕捉到导致故障的跟踪数据,并将此数据转换为模拟组可用的激励文件。反过来说,模拟组可以根据它在设计中所发现的危险,给系统组发出提醒。在两个工作于不同环境的验证组间建立联系是LSI公司两方向测试方法的关键。在整个过程中,两个组会交换数据,而且,最后设计晶粒需要两个组的结论。

一种可为大家接受的方法

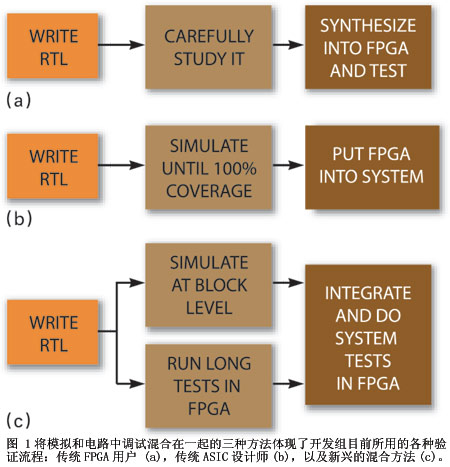

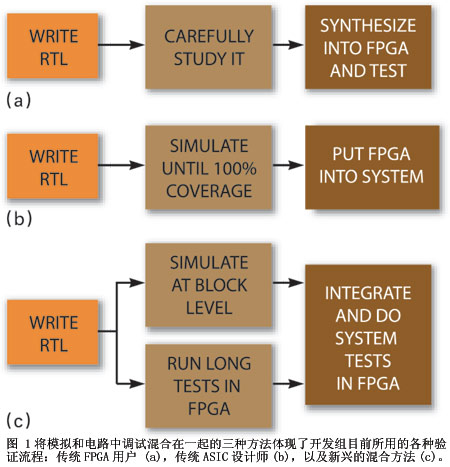

根据与FPGA厂商和用户的讨论,我们可以看到对模拟和仿真(图1)混合验证流程大家基本达成一致意见。这种流程首先对设计开始元件块级的模拟——不是传统上ASIC所用的那种穷举式的力求完美的模拟,而更像是对实际情况进行检查。其目标是验证元件块可用、引脚工作基本正确、在实验环境中可满足FPGA 的时序需要。

在此阶段,很多开发组将某个版本的块转入FPGA并开始更为彻底的电路中测试。如果此电路块(如视频编解器)需要很长的高速数据流来验证功能或是包括高速I/O功能,则该方法尤为常见。在其他情况下,继续对块进行模拟工作,直到所有问题都经过验证,可以进行集成为止。

根据大家的一致意见,当开发组开始将块集成时——建立试验系统时——FPGA 才真正被更多人使用。这里,可能就是因为设计太大才无法进行快速模拟,或是对于已知可正常工作的块,在FPGA上解决集成问题可能要比在模拟器上效率更高点。

但是,根据大家的意见,从模拟转到仿真并不是单步的可逆步骤。正如软件开发中并行进行模拟一样,模拟工作在系统仿真期间也在继续。多数开发组利用FPGA 仿真捕捉和隔离缺陷,然后将其送回模拟组诊断。在FPGA上做详细诊断是非常痛苦的工作。

这里先总体叙述当前的情况,然后指出该方法的几个严重缺点。首先,在两个环境间来回传送测试平台数据很困难。似乎还没有方法可以将创建测试的模拟指令自动映射到实施同一测试的 FPGA 结构。第二,各大 FPGA 厂商都可提供的嵌入式RISC核资源似乎远没有得到充分利用,它可以管理数据和控制测试,但是又是与模拟测试平台分开的。理论上说,模拟组可以将其转为嵌入式处理器核的C代码,而不是转为FPGA的RTL。第三,没有简单的途径可以将FPGA 试验中开发组收集的数据送回模拟平台。最后,随着模拟领域基于断言的验证工作不断增多,FPGA 侧急需一种类似的基于断言的工具。

基于 FPGA的仿真系统销售厂商对这些问题提出了应对措施(见附文《解决覆盖空隙的一些思路》),证明了这些问题是确实存在的。这里的例子有Eve公司的系统;模拟加速器,如GateRocket;以及“big- iron”(大型的)仿真盒,如Cadence的Palladium。至于这个基础平台会发展为FPGA验证领域常见的那种专用板卡级仿真平台,还是仍然会是昂贵的加速器和仿真系统的一种变形,我们尚无法知道。

因此,简言之,每种方法都有优缺点。根据这些信息,有经验的ASIC设计组(即经常在其验证流程中采用FPGA者)是如何在模拟测试和基于FPGA的测试间做出平衡的呢?

视频处理器厂商Ambarella有一个例子来回答这个问题。执行副总裁Didier LeGall 说,“多数情况下,我们根本就不使用FPGA 仿真。根据我们的经验,必须得有非常成熟的RTL仿真才会有用。但是,目前流程阶段,将设计输入 FPGA和建立测试平台(的过程)是一件事倍功半的事。”

但是,实际应用情况可能会使LeGall 的看法有所调整。Ambarella 公司的SOC (片上系统) 用于以高帧速率处理高清视频和10M像素静止图像,需要采用非常快的内部时钟和复杂的算法。但是,LeGall 在对FPGA 仿真做出评论后,又对整个验证过程的目标提出了一个非常有趣的看法。“新推出IC成功的关键不在于完美的验证工作,” LeGal说。“而在于软件”:也就是说,要知道设计中哪部分比较容易出问题,并且在开始,而不是事后,就做好软件解决计划。这种策略下,验证工程师经过广泛的基于FPGA的测试所获得的很多信息的确会变得比较没用。

LSI Corp的存储元件部门提出了另一个观点。该部门的副总裁和总经理Bill Wuertz叙述了他们是如何做SCSI (小型计算机系统接口)和SAS (串行连接)控制器的。

Wuertz 说LSI采用了几乎是并行的过程,一个验证小组进行模拟实现一些目的,而另一组则采用FPGA实现另外一些目的。“在设计早期,我们建立一个称为试验 RTL(trial RTL)的步骤,” Wuertz 说。“我们要知道RTL基本工作正常、各个块互相已连接好,这是第一个点。在此阶段,验证工作分为两个方向。模拟小组编写他们的工具所用的设计,并继续对单个的块进行模拟。另一个组,即系统工程组,则通过综合RTL得到内部开发FPGA 版——我们现在正在设计第五代板卡——然后开始在系统级进行彻底的压力测试。”

如Wuertz所述,这两个组具有不同的工作目的。模拟组要努力确保电路正确。系统组通常不考虑电路,但要确保芯片在变化异常大和非常复杂的存储网络环境下可以工作。Wuertz 说FPGA 原型会与一屋子的磁盘和磁带驱动器相连运行几天的测试。“这些测试已经过了20多年的发展,”他说。“我们知道,可能需要对不同磁盘驱动器组合进行很长时间的测试后才可以产生暴露设计问题的时间匹配异常情况。”

LSI 已开发了自有的将两种环境联系起来的内部工具。例如,通过这些工具,系统组可以捕捉到导致故障的跟踪数据,并将此数据转换为模拟组可用的激励文件。反过来说,模拟组可以根据它在设计中所发现的危险,给系统组发出提醒。在两个工作于不同环境的验证组间建立联系是LSI公司两方向测试方法的关键。在整个过程中,两个组会交换数据,而且,最后设计晶粒需要两个组的结论。

一种可为大家接受的方法

根据与FPGA厂商和用户的讨论,我们可以看到对模拟和仿真(图1)混合验证流程大家基本达成一致意见。这种流程首先对设计开始元件块级的模拟——不是传统上ASIC所用的那种穷举式的力求完美的模拟,而更像是对实际情况进行检查。其目标是验证元件块可用、引脚工作基本正确、在实验环境中可满足FPGA 的时序需要。

在此阶段,很多开发组将某个版本的块转入FPGA并开始更为彻底的电路中测试。如果此电路块(如视频编解器)需要很长的高速数据流来验证功能或是包括高速I/O功能,则该方法尤为常见。在其他情况下,继续对块进行模拟工作,直到所有问题都经过验证,可以进行集成为止。

根据大家的一致意见,当开发组开始将块集成时——建立试验系统时——FPGA 才真正被更多人使用。这里,可能就是因为设计太大才无法进行快速模拟,或是对于已知可正常工作的块,在FPGA上解决集成问题可能要比在模拟器上效率更高点。

但是,根据大家的意见,从模拟转到仿真并不是单步的可逆步骤。正如软件开发中并行进行模拟一样,模拟工作在系统仿真期间也在继续。多数开发组利用FPGA 仿真捕捉和隔离缺陷,然后将其送回模拟组诊断。在FPGA上做详细诊断是非常痛苦的工作。

这里先总体叙述当前的情况,然后指出该方法的几个严重缺点。首先,在两个环境间来回传送测试平台数据很困难。似乎还没有方法可以将创建测试的模拟指令自动映射到实施同一测试的 FPGA 结构。第二,各大 FPGA 厂商都可提供的嵌入式RISC核资源似乎远没有得到充分利用,它可以管理数据和控制测试,但是又是与模拟测试平台分开的。理论上说,模拟组可以将其转为嵌入式处理器核的C代码,而不是转为FPGA的RTL。第三,没有简单的途径可以将FPGA 试验中开发组收集的数据送回模拟平台。最后,随着模拟领域基于断言的验证工作不断增多,FPGA 侧急需一种类似的基于断言的工具。

基于 FPGA的仿真系统销售厂商对这些问题提出了应对措施(见附文《解决覆盖空隙的一些思路》),证明了这些问题是确实存在的。这里的例子有Eve公司的系统;模拟加速器,如GateRocket;以及“big- iron”(大型的)仿真盒,如Cadence的Palladium。至于这个基础平台会发展为FPGA验证领域常见的那种专用板卡级仿真平台,还是仍然会是昂贵的加速器和仿真系统的一种变形,我们尚无法知道。

FPGA Xilinx Verilog 仿真 Altera 电路 PCB 嵌入式 Cadence 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)