自适应跳频电台跳频控制系统设计与实现

避扰(自适应)模块结构

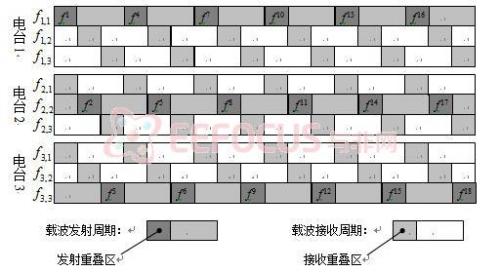

避扰性能的良好发挥建立在大部分电台已经入网的基础上。以三用户小型网络为例,电台工作时序图如下:

图4跳频局域网络通信系统的同步保持频率关系

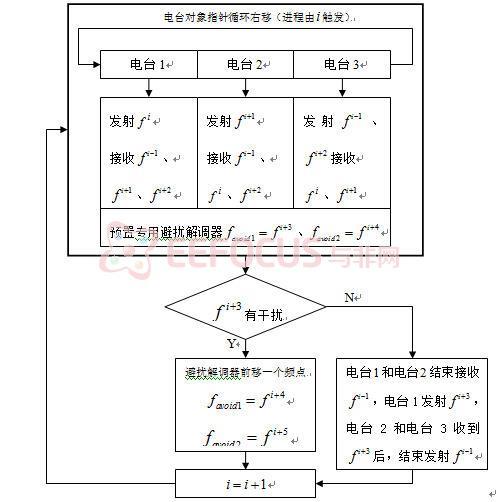

图 5 避扰流程图

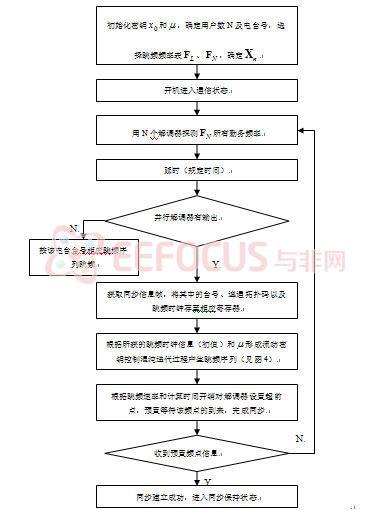

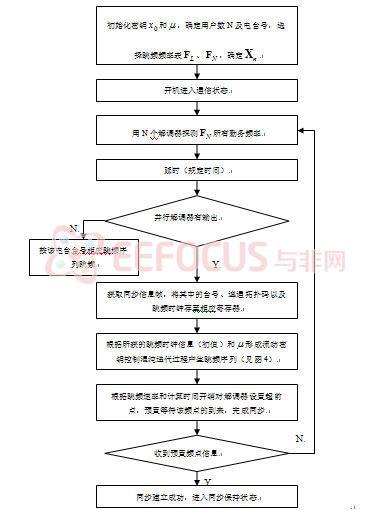

(3)同步建立流程图

根据自适应动态双频跳频理论,电台从开机到同步建立的工作流程图如下:

图6 自适应动态双频跳频同步建立流程图

其中延时程序中规定的时间具体值和系统计算时间的开销在FPGA实现时,由试验测定给出。

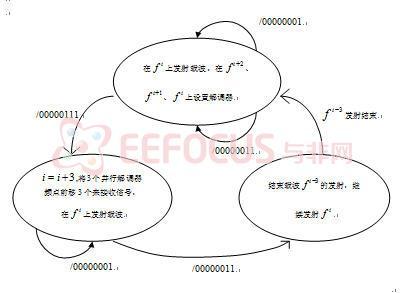

(4)同步保持状态下电台收发状态转换图(以三电台为例)

根据自适应动态双频跳频理论,任一部电台在发射信息期间,网内电台处于接收信息的状态。3部电台每部电台应配置5个解调器,其中3个解调器用来解调各电台的已调信号,另外两个在避扰时用来探测干扰频率。在系统设计中设计一专用寄存器实时读取此三个解调器的状态。例如:在电台1发射![]() 期间,电台2和电台3在它的并行解调器上收到信息且完成解调,那么该寄存器值为00000001;电台2发射

期间,电台2和电台3在它的并行解调器上收到信息且完成解调,那么该寄存器值为00000001;电台2发射![]() 期间,根据双频跳频规则,此时

期间,根据双频跳频规则,此时![]() 仍存在信道中,那么电台1和电台3在其并行解调器上收到信息并完成解调,解调器状态寄存器值为00000011。各电台根据寄存器状态的值决定是否发送下一频率,其状态转换图如下:

仍存在信道中,那么电台1和电台3在其并行解调器上收到信息并完成解调,解调器状态寄存器值为00000011。各电台根据寄存器状态的值决定是否发送下一频率,其状态转换图如下:

图 7 同步保持状态下电台收发状态转换图

4、电台主要技术参数及系统框图

(1)跳频主要技术参数。

信道间隔:25khz,跳速:516hops/s,数字话音传输速率16kbit/s。考虑到实际传送数据率的计算需要的包括换频、数据保护等开销,约占数据率的20%左右,即在实际信道中传送的数据率约为20kbit/s,由此可得带宽效率![]() ,可以满足系统带宽要求。

,可以满足系统带宽要求。

图 8 系统实现逻辑框图

(2)系统功能描述(参照图8)

系统建立了三个用户,其中用户1发送信息为系统板采集的话音信号,用户2和用户3发送随机二进制信号。用户1接收来自用户2的随机二进制数,用户3接收来自用户1的话音信号。系统功能实现后,用户1的接收机输出和用户2的发送信息相比较,可以计算系统误码率。通过电台3的话音输出可懂度可以检验该系统的实际通话质量。通过编写上位机软件,可以利用USB接口对跳频参数进行设置。

(3)系统模块介绍(参照图8)

本设计拟完成的工作包括:在Virtex-II PRO(V2-Pro)开发系统上构建完整的自适应双频跳频通信系统,编程实现发射机、接收机的各种基带信号处理算法,编程实现跳频同步控制和避扰功能,并对AWGN信道、Rice平坦衰落信道、Rice频率选择性衰落信道、Rayleigh平坦衰落信道和Rayleigh频率选择性衰落信道等五种信道环境进行软件模拟,通过程序模拟实际信道的非理想情况,对真实的无线通信环境作抽象和近似,以此验证系统设计的正确性。

要实现的主要模块包括:

(1)数据的采集和输出模块

对于话音信号,利用开发系统自带的音频I/O接口和音频解码芯片LM4550(符合AC97标准)完成;通过USB接口,在PC和开发板之间完成数据交换。

(2)接收与发送缓冲模块

设计合理的缓冲区结构,对接收和发送的数据进行缓冲存储,使数据收发和数据处理并行完成。

(3)基带信号处理模块

包括散布电台的收发信机、跳频同步控制以及避扰三部分,实现图2中各种信号处理算法。

(4)信道建模与仿真模块

通过USB通道或者DIP开关将信道参数传给FPGA,FPGA调用相应的函数模拟信号通过信道的传输过程。

自适应 电台 跳频控制 混沌系统 Logistic 相关文章:

- 智能天线技术及其应用(02-10)

- 不采用自适应算法的智能天线系统(01-19)

- 基于智能天线技术的TD—SCDMA系统用研究(05-01)

- 蜂窝电话功率放大器的天线接口的自适应调谐技术(07-26)

- 蓝牙和Wi-Fi共存在智能手机上的两种解决方法对比(08-28)

- 无线产品功率放大器-天线接口的自适应调谐设计(11-28)