飞兆半导体AX-CAP 技术

摘要: 本文介绍了飞兆半导体 mWSaver 技术中的一项功能,即 AX-CAP 放电功能,它实现了无负载和轻负载条件下业内最佳的最低功耗,并符合 2013 能源之星和 ErP 规范。 这项创新的技术通过消除 X 电容放电电阻最大限度地减少 EMI 滤波器的功率损耗,同时满足 UL1950 的安全要求。

I.引言

近年来,节能一直是对电器的关注重点,特别是在待机功耗方面。 为了最大限度地降低功率损耗并符合最新能源之星规范和 2013 ERP ErP 待机功率规定(ATX 电源和 LCD TV 电源在 0.25W 负载下小于 0.5W 的功耗),飞兆半导体已经开发了若干项创新技术,以提高空载和轻负载条件下的节能性能。

其中的主要损耗之一是由于并联到 EMI 滤波器 X 电容的放电电阻造成的,如图1所示。 根据安全法规,如 UL1950 和 IEC61010-1,需要使用电阻,这就需要电容在电源插头从电源插座拔下后的给定时间内放电至安全电平。

图1.线路 EMI 滤波器的典型电路

UL1950:对于 A 类设备,电容中大于 0.1μF 的电压必须在 1 秒内衰减到交流 输入峰值电压的 37%;对于 B 类设备,必须在 10 秒内完成。

IEC61010-1:电源断开 5 秒后,引脚不得处于危险状态(通电)。

1)

2)

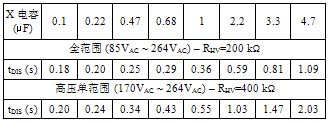

表格 1 表明了不同的额定功率系统和放电电阻功率损耗之间的关系。 随着功率的上升,EMI 滤波器的电容也会增加,因此,需要更小的放电电阻以保持相同的放电时间。 这通常会导致高功率应用中更多的功率损耗。 放电电阻的功率消耗是高功率应用中待机功耗的主要原因之一。

表格 1.不同额定功率系统的放电电阻功率损耗

创新的 AX-CAP™ 放电方法是飞兆半导体公司的一项专有 mWSaver™ 技术,旨在取消使用 X 电容放电电阻,同时满足安全要求。

II.提议的解决方案

开关模式电源前端的 EMI 滤波器通常包含贯穿交流线路连接器的电容,如图2所示。 诸如 UL1950 和 IEC61010-1 等安全法规要求电容在电源插头从电源插座拔下后的给定时间内放电至安全电平。 通常,在电容上并联放电电阻,用于确保电容已放电,但这会造成电源的功率损耗。 飞兆半导体 FPS™ (飞兆电源开关)FSB 系列的创新 AX-CAP™ 技术仅在电源插头从电源插座上拔下时对滤波器电容有效放电。 由于在正常操作中,AX-CAP 放电电路被禁用,因此 EMI 滤波器的功率损耗几乎完全消除。

图2.FSB 系列的 AX-CAP™电路连接

在图3中,拔出插头时,(VAC)X电容上的交流电压通过HV引脚采样慢慢放电。 FSB 系列对 HV 引脚采样,检测所连接的 X 电容上的交流电压状态,如Fig. 2所示。 FSB 系列设置了阈值电压,用于检查 X 电容上的交流电压是否一直高于阈值电平(大约 ½ V交流电峰值),同时在去抖动时间内无零交叉。 满足这个条件后,FSB 系列进入放电模式,并打开采样开关。 X 电容上的电压通过 HV 引脚采样路径放电。

图3.从电源插座上拔出电源插头时的 HV 引脚行为

III.最糟情况分析

拔出电源插头后的放电时间,可由等式 (3) 和 (4) 计算得出:

3)

4)

其中:

VDIS-ST:X 电容进入放电模式的电压电平;

VDIS-EN:X 电容满足安全要求时(交流峰值电压的 37%)的电压电平;

tAC-OFF:AX-CAP™ 检测线电压的去抖动时间;

tS-TIME:HV 引脚采样周期;

tS-CYCLE: HV 引脚采样频率。

最糟情况下FSB系列的放电时间VCXTable 2=373V计算如所示,VDIS-EN=138V。此处,tAC-OFF 为 160 ms,tS-TIME 为 20 µs,tS-CYCLE 为 960 µs。 RHVFig. 4取决于不同的交流输入电压范围;因此最糟情况分析如所示。

表格 2.264 V 交流输入电压下,不同 X-CAP™的最糟放电时间

图4.FSB 系列放电时间最糟情况分析

IV.实验结果

对 300W ATX 电源中 16W/5V 待机功率的测试表明提议的方法行之有效。 图 5 显示了在以下条件下使用 AX-CAP™ 放电方法的实验结果:

| X-cap™: | 0.47 µF |

| RHV: | 200 kΩ |

飞兆 半导体 电容 电阻 滤波器 LCD 电路 电压 连接器 开关电源 相关文章:

- 用于低成本高效率离线LED驱动器的初级端调节技术(05-14)

- 通过初级端调节满足充电器能效规范(10-29)

- 大功率LED照明恒流驱动电源的设计(10-15)

- 利用低端栅极驱动器IC进行系统开发(12-21)

- 选择高压场效应管实现节能(06-13)

- 确定功率MOSFET的适用性(07-27)