创新的低待机损耗解决方案应用于反激式转换器

时间:09-10

来源:互联网

点击:

FAN6756 与 FAN6754无载损耗计算实例

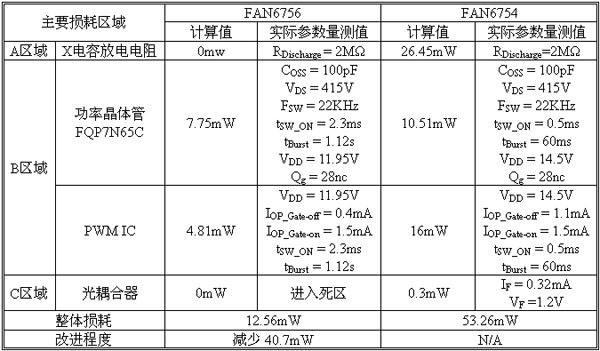

将飞兆半导体新、旧PWM IC:FAN6756 与FAN6754 置于相同的测试板上 (其额定输出电压/电流规格为19V/3.42A),量测无载时与输入电压为230V时的相关参数值,并将这些实测参数带入表一中所提的无载损耗计算式, 可得到如表三所计算的损耗值。以前的 PWM IC (FAN6754) 并没有集成飞兆半导体的创新节电技术,所测得的无载损耗为 73mW。

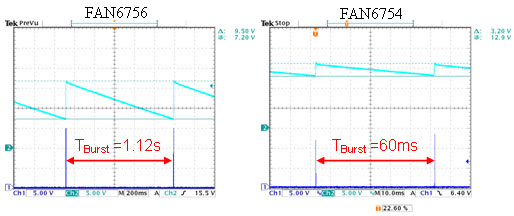

图九、输入230 VAC 的无载测试波形 (Ch1-Gate Ch2-VDD)

表三、FAN6756 与 FAN6754 无载的主要损耗计算表(不含变压器损耗)

结论

本文章探讨FAN6756降低电源供应器整体待机功率损耗的方法。首先以数学表示式大约表示出主要的开关损耗和控制电路损耗,进而确认降低开关频率 (FSW) 与增加栅极脉冲时间 (tBurst) 为降低功率晶体管功耗的主要对策,接着导入多项飞兆半导体创新的专利技术去实现更低的整体待机损耗。最后,应用于一款实际的交流反激式转换器系统中,其额定输出电压/电流规格为19V/3.42A,在230V 交流输入且于输出无载时,输入功率只有30mW。

飞兆 半导体 电子 电路 电流 电容 电阻 变压器 电容器 电压 比较器 电路图 PWM 二极管 相关文章:

- 用于低成本高效率离线LED驱动器的初级端调节技术(05-14)

- 通过初级端调节满足充电器能效规范(10-29)

- 大功率LED照明恒流驱动电源的设计(10-15)

- 利用低端栅极驱动器IC进行系统开发(12-21)

- 选择高压场效应管实现节能(06-13)

- 确定功率MOSFET的适用性(07-27)