EDGE手机基带处理设计的几种实现方法评估

时间:12-10

来源:互联网

点击:

在无线市场上,EDGE协议已迅速为业者所接受,EDGE手机设计中支持多时隙传输、多种调制解调器/语音编译码器是基带处理面临的最大挑战。如何以高性能价格比方式实现EDGE的基带部分并占据最小的PCB面积最小?目前有几种实现方法,本文将对这些方法的技术优缺点和风险进行评估,中国手机设计工程师和手机芯片设计工程师应予以关注。

EDGE通常称为2.5G的规范,并且被人们看作向3G系统过渡的标准,诸如宽带码分多址(W-CDMA)。通过实现EDGE协议,目前北美的时分多址(TDMA)移动通信系统和全球通(GSM)系统的开发者可以设计具有384Kbps数据率的手机。这使得一个小小的手机同时满足话音通信、因特网接入以及多媒体内容的要求成为可能。开发EDGE基带手机的工程师们将会面对一系列设计上的挑战。具体来说,在开发EDGE无线手机的基带部分时,工程师要遇到很多难点和新的设计方法问题。

目前的解决方案

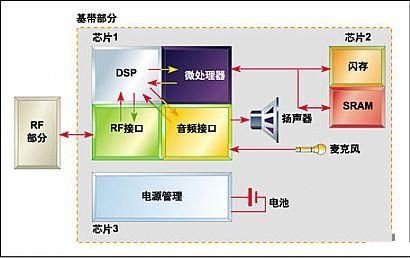

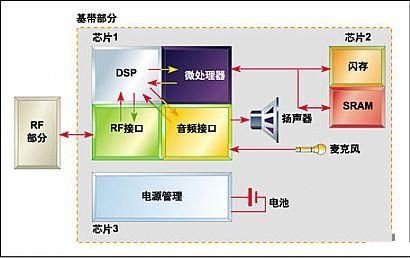

为了详细地评估EDGE无线手机设计的基带结构,首先研究一下当前TDMA手机设计采用的基带结构至关重要。图1中标明的TDMA基带部分可以分成七大块。第一块包括射频(RF)到基带的接口。从基站到移动台间的下行传输链路中,RF信号以最小奈奎斯特速率进行数字化。在上行链路中,处理过程则相反,来自数字信号处理器(DSP)的数字化取样信号被转化为模拟信号。

第二块包括配备ROM、RAM的DSP芯片,以及协处理器。在这些组件中,DSP是基带模块的核心,它执行多种与协议物理层对应的计算强度要求高的功能

为突出该DSP的重要性,在处理一个对MIPS要求高的数字信道(DTC)时,应该对该组件的主要任务进行检测。在TDMA设计中,处理一个DTC接收时隙过程中,DSP首先进行“粗同步”,以寻找该时隙中的SYNC字。这样做是为了建立粗略的时间基准、频率误差和自动增益控制(AGC)的设置。接着处理器执行“精确同步”,建立均衡器的定时标志和初始信道系数。如果该信道传输有很大延迟,则采用一个微分检波器或均衡器对P/4微积分相移键控(DQPSK)信号进行解调。

该DSP接着将进行数字确认色标编码(DVCC)以及低速访问控制信道(SACCH)的序列解码。DVCC是一个确认收到正确的基站信号的参数。SACCH是在同一个时隙内作为话音信号或快速访问控制信道(FACCH)发送的低速控制信息。然后,进行话音/FACCH分离和解码。这些功能与传输端完成的交织和信道编码相对应,表现为时间分散性和误码率(BER)。

DSP还进行语音解码、回波对消、语音编码、SACCH信道编码/交织、语音/FACCH编码和交织,以及脉冲群格式化(burst formatting)。在脉冲群格式化阶段,数据位和其它数据块,如SYNC、SACCH和CDVCC将被格式化以便占据324位IS-136时隙中的正确位置。

在TDMA设计中,如果工程师们用一个协处理器进行一部分信道解码,他们可以把所需的5MIPS减少到大约2MIPS。此外,要注意一些较小运算项也需要消耗额外的MIPS,因此一个第二代IS-136 DSP需要大约37MIPS的处理能力。

在基带设计中,DSP由一个微处理器辅助工作,它被用来优化决策导向码(decision-directed code)并且感知、控制外部事件。此嵌入式处理器提供DSP的接口层、Layer2和Layer3协议,以及用户接口软件。IS-136需要的处理能力要求微处理器工作在10MHz左右。

其它各模块简介

音频接口是传统TDMA基带结构的另一模块。这个接口包括8kHz语音编码、滤波器和放大器。音频接口之后是功率管理模块,它支持的主要功能有电池充电及监控、全部基带电路和RF的电压调节器、开机控制、LED驱动器以及振荡器。

TDMA蜂窝电话基带部分的最后模块专用于存储。首先是快闪存储模块,存储所有微处理器编码。典型的IS-136手机需要16Mb快闪存储空间,这取决于所支持的应用软件。然后是静态存储器(SRAM)模块,用作缓存、寄存器和中间存储器。该存储模块在TDMA手机设计中占2Mb空间。

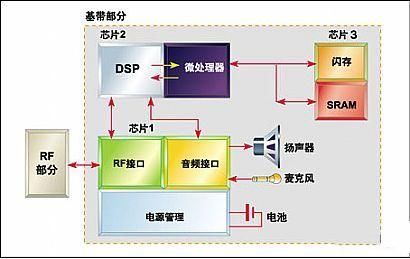

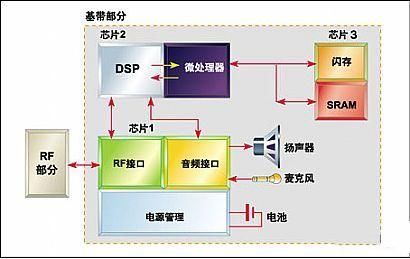

目前基带的集成功能大部分由三个集成芯片和若干分立元件实现。最主要的集成芯片实现方式有两种:一种是所有模拟功能集中在一个芯片上,DSP和微处理器集成在另一个芯片上,存储器件则在最后的集成芯片上(图2);另一种是射频RF接口、音频接口、DSP和微处理器都在一个芯片上,存储模块在第二块芯片上,电源管理功能在最后一块芯片上实现(图3)。

这两种实现方式各有其优点和缺点。在第一种设计中,其主要的优点是将模拟功能组合到一个单一芯片上,通过将所有的模拟功能捆绑在一起,容易应用先进的技术工艺。其缺点是要求DSP放在一个单独的芯片上,因此,设计者需解决RF接口和DSP之间以及音频接口和DSP之间的联接线。这将占据PCB的布线空间、增加额外噪声并在驱动这些线上的电容时产生功率损耗。

在第一种实现中,功率管理功能也是一个问题,其功率管理功能是和附加电路结合在同一个IC上的。这会引起封装设计中的散热处理问题。最后一点,工作在IS-136子帧速率下的固定电压调节器会在音频电路中引起噪声。

第二种设计同样也有长处和短处。好的方面,就是它能很好地将RF接口、DSP和音频接口的连接做在同一芯片上。通过单一芯片上的这种功能组合,设计人员可以改善PCB的布线空间以及这些模块间的信息传递。差的方面,就是模拟电路和数字电路合在同一芯片上。因此,实现该功能的芯片会存在布局和隔离问题。而且,由于模拟电压的变化落后于数字电压,这种拓扑结构不利于工程师采用先进的数字工艺。

EDGE通常称为2.5G的规范,并且被人们看作向3G系统过渡的标准,诸如宽带码分多址(W-CDMA)。通过实现EDGE协议,目前北美的时分多址(TDMA)移动通信系统和全球通(GSM)系统的开发者可以设计具有384Kbps数据率的手机。这使得一个小小的手机同时满足话音通信、因特网接入以及多媒体内容的要求成为可能。开发EDGE基带手机的工程师们将会面对一系列设计上的挑战。具体来说,在开发EDGE无线手机的基带部分时,工程师要遇到很多难点和新的设计方法问题。

目前的解决方案

为了详细地评估EDGE无线手机设计的基带结构,首先研究一下当前TDMA手机设计采用的基带结构至关重要。图1中标明的TDMA基带部分可以分成七大块。第一块包括射频(RF)到基带的接口。从基站到移动台间的下行传输链路中,RF信号以最小奈奎斯特速率进行数字化。在上行链路中,处理过程则相反,来自数字信号处理器(DSP)的数字化取样信号被转化为模拟信号。

第二块包括配备ROM、RAM的DSP芯片,以及协处理器。在这些组件中,DSP是基带模块的核心,它执行多种与协议物理层对应的计算强度要求高的功能

为突出该DSP的重要性,在处理一个对MIPS要求高的数字信道(DTC)时,应该对该组件的主要任务进行检测。在TDMA设计中,处理一个DTC接收时隙过程中,DSP首先进行“粗同步”,以寻找该时隙中的SYNC字。这样做是为了建立粗略的时间基准、频率误差和自动增益控制(AGC)的设置。接着处理器执行“精确同步”,建立均衡器的定时标志和初始信道系数。如果该信道传输有很大延迟,则采用一个微分检波器或均衡器对P/4微积分相移键控(DQPSK)信号进行解调。

该DSP接着将进行数字确认色标编码(DVCC)以及低速访问控制信道(SACCH)的序列解码。DVCC是一个确认收到正确的基站信号的参数。SACCH是在同一个时隙内作为话音信号或快速访问控制信道(FACCH)发送的低速控制信息。然后,进行话音/FACCH分离和解码。这些功能与传输端完成的交织和信道编码相对应,表现为时间分散性和误码率(BER)。

DSP还进行语音解码、回波对消、语音编码、SACCH信道编码/交织、语音/FACCH编码和交织,以及脉冲群格式化(burst formatting)。在脉冲群格式化阶段,数据位和其它数据块,如SYNC、SACCH和CDVCC将被格式化以便占据324位IS-136时隙中的正确位置。

在TDMA设计中,如果工程师们用一个协处理器进行一部分信道解码,他们可以把所需的5MIPS减少到大约2MIPS。此外,要注意一些较小运算项也需要消耗额外的MIPS,因此一个第二代IS-136 DSP需要大约37MIPS的处理能力。

在基带设计中,DSP由一个微处理器辅助工作,它被用来优化决策导向码(decision-directed code)并且感知、控制外部事件。此嵌入式处理器提供DSP的接口层、Layer2和Layer3协议,以及用户接口软件。IS-136需要的处理能力要求微处理器工作在10MHz左右。

其它各模块简介

音频接口是传统TDMA基带结构的另一模块。这个接口包括8kHz语音编码、滤波器和放大器。音频接口之后是功率管理模块,它支持的主要功能有电池充电及监控、全部基带电路和RF的电压调节器、开机控制、LED驱动器以及振荡器。

TDMA蜂窝电话基带部分的最后模块专用于存储。首先是快闪存储模块,存储所有微处理器编码。典型的IS-136手机需要16Mb快闪存储空间,这取决于所支持的应用软件。然后是静态存储器(SRAM)模块,用作缓存、寄存器和中间存储器。该存储模块在TDMA手机设计中占2Mb空间。

目前基带的集成功能大部分由三个集成芯片和若干分立元件实现。最主要的集成芯片实现方式有两种:一种是所有模拟功能集中在一个芯片上,DSP和微处理器集成在另一个芯片上,存储器件则在最后的集成芯片上(图2);另一种是射频RF接口、音频接口、DSP和微处理器都在一个芯片上,存储模块在第二块芯片上,电源管理功能在最后一块芯片上实现(图3)。

这两种实现方式各有其优点和缺点。在第一种设计中,其主要的优点是将模拟功能组合到一个单一芯片上,通过将所有的模拟功能捆绑在一起,容易应用先进的技术工艺。其缺点是要求DSP放在一个单独的芯片上,因此,设计者需解决RF接口和DSP之间以及音频接口和DSP之间的联接线。这将占据PCB的布线空间、增加额外噪声并在驱动这些线上的电容时产生功率损耗。

在第一种实现中,功率管理功能也是一个问题,其功率管理功能是和附加电路结合在同一个IC上的。这会引起封装设计中的散热处理问题。最后一点,工作在IS-136子帧速率下的固定电压调节器会在音频电路中引起噪声。

第二种设计同样也有长处和短处。好的方面,就是它能很好地将RF接口、DSP和音频接口的连接做在同一芯片上。通过单一芯片上的这种功能组合,设计人员可以改善PCB的布线空间以及这些模块间的信息传递。差的方面,就是模拟电路和数字电路合在同一芯片上。因此,实现该功能的芯片会存在布局和隔离问题。而且,由于模拟电压的变化落后于数字电压,这种拓扑结构不利于工程师采用先进的数字工艺。

PCB 射频 DSP MIPS 嵌入式 滤波器 放大器 电路 电压 LED 振荡器 电源管理 电容 模拟电路 编码器 仿真 总线 相关文章:

- 精密计时——自动化与大众化(10-22)

- 手机、相机、液晶显示屏抗电磁干扰特性的实现(11-26)

- 针对有线电视和通讯应用的PIN二极管衰减器的结构(11-22)

- 详细分析背光各材料的功用 (11-29)

- 利用约束管理来简化印刷电路板设计(02-14)

- 基于NXP UOCIII芯片的LCD TV方案 (04-17)