针对有线电视和通讯应用的PIN二极管衰减器的结构

时间:11-22

来源:电子系统设计

点击:

可调衰减器在各种通讯应用中是有用的器件,例如,衰减器可用来控制收发器的信号水平,特别是在许多现代通讯系统中,高线性度是一个关键的要求,使用一只安华高科的低成本SOT-25表面贴装二极管四元组,就可以构造一个简单的电压控制衰减器,这个简单的衰减器在0.3~3000MHz的宽频段仍然具有出色的线性特性。

这种衰减器不仅非常适合于有线电视(CATV)网络和CATV机顶盒,在甚高频无线及蜂窝通讯设备及低频微波通讯、特别在空间有限而不能使用分布式元件的应用中也非常有用。

安华高科的HSMP-3816二极管四元组采用5脚无引线SOT-25表面贴装型封装。π结四元组PIN二极管由从同一晶片挑选的、电气特性密切匹配的毗连元件组成。在封装的四元组中,脚1和脚3用于RF输入/输出,脚2用来为二极管提供偏压,脚4、5用来提供分路偏压。除了尺寸方面的优势外,与四个分离元件组成的四元组相比,将四个性能完全匹配的PIN二极管捆绑到SOT-25封装中有助于保证衰减器的输入输出臂之间具有更好的对称性。

用两个并联电阻和一个串联电阻就可以构造一个基本的pi配置固定电压衰减器,通过配置即可以得到A=20log (K)的衰减,同时提供能够匹配具体应用电路特性阻抗的输入/输出阻抗。在工作频率高于衰减器截止频率的情况下,一个PIN二极管可以做为电流控制可变电阻使用。不过,只有在工作频率完全高于二极管的截止频率fc=1/2πτ的条件下这个电流控制变阻模型才比较精确,这里τ为器件中少数载流子的生命周期。在工作频率10倍于fc时,一个PIN二极管就可以精确地用一个具有恒定微值结电容的电流控制并联电阻来模拟。工作频率低于0.1fc时,PIN二极管就表现为一个普通的PN结二极管。

工作频率在0.1fc到10fc之间时,PIN二极管的特性就变得非常复杂,一般表现为一个与一个高频电流电感或电容并联的、随频率变化而变化的电阻。另外,工作在这个范围内时,信号失真畸变也非常严重。对于HSMP-3810型二极管而言,τ≈1500ns,其截止频率为1,000kHz,因此在1000kHz以上二极管的电阻值与工作频率无关,不过,由于已经针对宽带衰减器应用对此二极管进行了优化,所以即使在fc以下此二极管也具有良好的特性。

可以用三个二极管来代替pi电路中的固定电阻,构造一个可变衰减器,不过,这样会导致网络中的不对称,从而导致产生一个相当复杂的偏压网络。用两个PIN二极管来代替其中的串联电阻可以获得几个性能方面的好处。首先,由于串联二极管具有容性电抗而使网络与其它部分相隔离,用两个二极管代替一个电阻可以提高最大衰减值或在一定衰减值的条件下使频率上限翻倍。其二,代替串联电阻的两个二极管是180度反接的,这样就抑制了偶数次信号畸变的产生。其三,由此而得到的衰减器网络是对称的,从而可以大大简化偏压网络。电源电压V+是一固定电压,Vc是控制网络衰减的可变电压,用两个二极管代替电阻的唯一缺点是可能会增加介入损耗。

四元二极管pi型衰减器需要一个恒定的电压V+和一个可变的控制电压Vc。对于1.25V的V+,可变控制电压的范围为0V到大约5V。电压V+的值代表了回程损耗与控制电压范围之间的一个折衷,更低的V+可以降低回程电压,但同时也会使控制电压的工作范围缩小。

本文中介绍的衰减器是在8mm厚的RF4型印刷电路(PCB)上实现的。RF4具有良好的机械稳定性和耐久性,成本低,但其损耗大,难于控制,而且介质系数与工作频率密切相关。另一方面,玻璃纤维增强型聚四氟乙烯(PTEE)PCB材料具有良好的高频特性,但是相对昂贵一些,机械稳定性也比较差,不适合于某些表面贴装工艺。选用针对高频工作要求进行了优化的PCB基底材料可以改善高频性能,各种测量参数对频率的依赖程度受到与HSMP-3816二极管四元组、PCB、其它元件及连接器相关的寄生效应的影响。

将PIN二极管用做衰减元件时,PIN二极管具有比等效的GaAs MESFETs更高的线性度,通过使用具有厚I层及低介质张弛频率(fdr)的多个PIN二极管就可以将信号畸变减小到最低程度。在Avago公司PIN二极管产品线中HSMP-381x系列产品的I层最厚。在低衰减状态,大部分RF能量仅仅是从输入端传输到输出端而已。不过在高衰减状态,更多的RF能量被倾入衰减器,会使信号失真度上升。当Vc接近0时,几乎没有电流流过两个串联的二极管,它们接近于零偏压状态,其结电容将随RF电压同步变化,幸运的是,由于两个二极管是反向串联的,所以可以抑制由受RF调制的电容所产生的某些失真或畸变。由于封装的两个反串二极管具有完全互相匹配的特性,因此可以得到最佳的失真抑制能力。

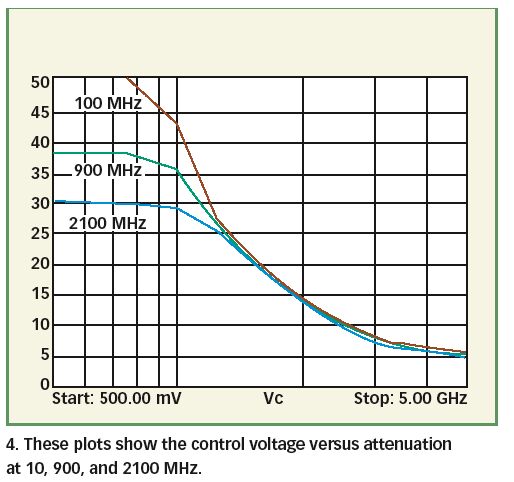

Pi衰减器的相位偏移随衰减值而变化。总的相位偏移接近90度,在三个相隔较远的工作频率点(100、900和1800 MHz)测试时此相位偏移表现相当稳定。

图1所示为π衰减电路的示意电路图。图2的左边为π衰减器的PCB布局,右边为元件布置。表1中给出了所需要的元件(包括四元二极管)。图3、4、5给出的成品π衰减器测试性能的样本。

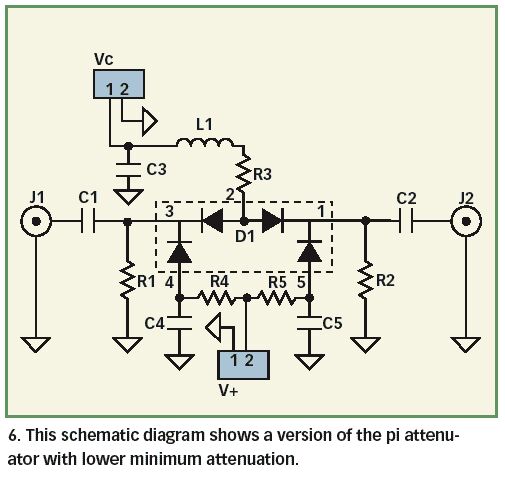

增加通过串联二极管的电流可以降低衰减下限。将控制电压保持在最大值5V,减小电阻R3的阻值就可以增大偏移电压,这可以通过给阻断RF的电阻R3(表2)串联一个表面贴装铁酸盐珠状电感而实现。在整个频率范围内,与传统的瓷芯多层片状电感相比,这种铁酸盐珠状电感具有更高的阻抗。图6给出了低衰减下限衰减电路的示意图,图7中给出了在Vc=5V的条件下与标准衰减电路的比较结果。

为了建立π衰减器的性能模型以便于进一步分析,安捷伦公司的高级设计系统(ADS)计算机辅助工程(CAE)软件为工程师们提供了模拟四元二极管π衰减器性能的技术支持范例。相应文件可以从www.edasupportweb.soco.agilent.com.的Agilent Eesof知识中心的"Examples"部分下载。

另外,包含在高频建模工具APLAC CAE软件包(www.aplac.com)中的PIN二极管模型也可以预测在给定正向偏移的条件下RF阻值。图8的左边给出了HSMP-3816 PIN二极管的APLAC模型,将APLAC模型与SOT-25等效电路模型(图8右边)结合在一起,就可以使设计人员在模拟过程中研究分析封装的寄生效应。

作者:Lim Chin Leong, Lim Yeam Ch'ng, Goh Swee Chye

- GPON打造家庭光世代(05-24)

- IPTV与互动电视主要技术模式的探讨(11-14)

- 触摸屏的应用与工作原理(10-23)

- SHARC处理器在音频系统中的应用(02-12)

- 业界首款支持 SPICE 模型的 SAR ADC(04-24)

- 基于ADS5294:80MSPS 8路医学图像解决方案(06-10)