高分辨率全帧CCD芯片FTF4027M的驱动电路设计

时间:09-11

来源:互联网

点击:

3.1 CCD所需的一些偏置电压

①VNS:加到CCD的N型基底上的电压,电压范围从22V到28V,主要用于控制CCD的高光行为(Antiblooming抗晕)。为了实现电荷复位功能,CR脉冲必须加到VNS上,这个电荷复位脉冲的主要功能是将CCD上已经积累好的光生电荷全部移除,这在CCD新的光积分循环开始时是必须的。

②SFD:加到CCD的输出放大器上的直流电压。

③RD:加到复位管(Reset Fet)上的直流电压。

④OG:连接SG和浮置扩散电容的输出栅上所加的电压。

⑤VPS:加到P掺杂基底上的电压。

3.2 CCD所需的驱动时序的设置

3.2.1 快门及光积分的控制时序

本款CCD属于全帧CCD,光敏面占CCD面积的大部分,为了得到100%的无污染点图像,必须加上机械快门。如图3所示,机械快门的开启由Trig-in信号完成。当Trig-in信号的上升沿到来时,触发快门使之进行开启动作,CCD准备进行光积分。在Trig-in信号上升沿之后,当基准时钟信号SSC的第一个上升沿到来时产生一个脉冲信号CR,用于对CCD进行初始化,CR脉冲宽度等于SSC的一个周期,为190.6μs。在SSC的下一个上升沿到来时,产生CR下降沿,这时快门彻底打开,CCD正式进入光积分阶段。当Trig-in信号的下降沿到来时,CCD光积分结束,同时触发机械快门使之进行关闭动作,在一个SSC周期的时间之后,快门完成关闭,然后再在SSC的上升沿到来的开始进行帧转移。因此机械快门的开启和关闭的动作总是落后于控制信号,这样就避免了在快门打开阶段就进行光积分,导致有用信号的丢失,也避免了因快门未完全关闭就开始进行帧转移而引起的图像噪声干扰。通过设置CR信号下降沿到Trig-in下降沿这段时间来控制光积分,也就控制了水平常说的电子快门速度。

3.2.2 垂直行转移的驱动时序

该时序涉及A1、A2、A3、A4、TG,其频率都为50kHz。SSC上升沿到来时标志着一次水平像素转移的结束和一次垂直行转移的开始,可通过控制四相A时钟信号的高低电平转换来完成。四相A时钟信号要满足严格的交迭原理,占空比为5:8,即五个单元的高电平和三个单元的低电平,所以相邻时钟信号之间的延迟为二个单元。A时钟信号的高电平有两个水平,分别用于CCD的不同工作状态,垂直转移状态的高电平要保持在14V,而光积分和保持状态高电平要保持在10V。TDA9991中集成了一个电平控制单元,可以完成对A时钟信号的电平控制。而在电平像素转换期间,A1必须继续保持低电平,A2、A3、A4保持高电平,从而保证光敏面中的未输出信号继续保持在A2、A3、A4电极之下。

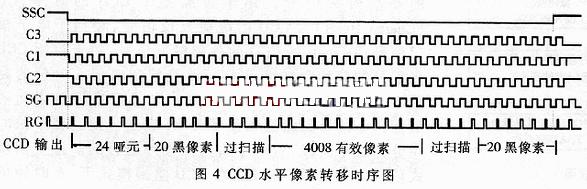

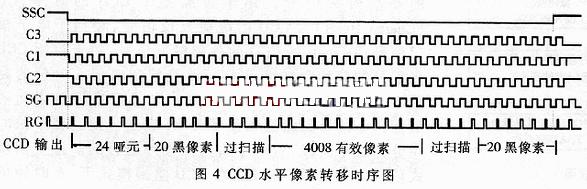

3.2.3水平像素转移的驱动时序

该时序涉及C1、C2、C3、RG、SG,其频率都为25MHz。SSC下降沿到来时标志着一次垂直行转移的结束和一次水平像素转移的开始,转移原理和行转移原理一样,三相C时钟信号要严格满足三相交迭原理,占空比为3:6,也就是高低电平保持时间一样。在电荷由光敏区向输出寄存器转移的过程中(见图4),在SSC下降沿到来之前,C3应该保持低电平,使像素在输出寄存器的隔离开来,而C1和C2应该保持高电平,使转移下隔断的电荷在这两个电极之下积聚起来,为下一步的水平转移输出作准备。

4 实验与讨论

系统设计完成后,根据CCD的时序村注,经仿真调试可以产生出相应的驱动脉冲和偏置电压。但是由于系统的后续图像处理和传输部分还没有设计好,所以无法进行图像采集。该驱动电路的研制结果表明,采用现在芯片进行系统设计有它自身的好处,可以简化设计,而且调试简单、可扩展性也比较强。

①VNS:加到CCD的N型基底上的电压,电压范围从22V到28V,主要用于控制CCD的高光行为(Antiblooming抗晕)。为了实现电荷复位功能,CR脉冲必须加到VNS上,这个电荷复位脉冲的主要功能是将CCD上已经积累好的光生电荷全部移除,这在CCD新的光积分循环开始时是必须的。

②SFD:加到CCD的输出放大器上的直流电压。

③RD:加到复位管(Reset Fet)上的直流电压。

④OG:连接SG和浮置扩散电容的输出栅上所加的电压。

⑤VPS:加到P掺杂基底上的电压。

3.2 CCD所需的驱动时序的设置

3.2.1 快门及光积分的控制时序

本款CCD属于全帧CCD,光敏面占CCD面积的大部分,为了得到100%的无污染点图像,必须加上机械快门。如图3所示,机械快门的开启由Trig-in信号完成。当Trig-in信号的上升沿到来时,触发快门使之进行开启动作,CCD准备进行光积分。在Trig-in信号上升沿之后,当基准时钟信号SSC的第一个上升沿到来时产生一个脉冲信号CR,用于对CCD进行初始化,CR脉冲宽度等于SSC的一个周期,为190.6μs。在SSC的下一个上升沿到来时,产生CR下降沿,这时快门彻底打开,CCD正式进入光积分阶段。当Trig-in信号的下降沿到来时,CCD光积分结束,同时触发机械快门使之进行关闭动作,在一个SSC周期的时间之后,快门完成关闭,然后再在SSC的上升沿到来的开始进行帧转移。因此机械快门的开启和关闭的动作总是落后于控制信号,这样就避免了在快门打开阶段就进行光积分,导致有用信号的丢失,也避免了因快门未完全关闭就开始进行帧转移而引起的图像噪声干扰。通过设置CR信号下降沿到Trig-in下降沿这段时间来控制光积分,也就控制了水平常说的电子快门速度。

3.2.2 垂直行转移的驱动时序

该时序涉及A1、A2、A3、A4、TG,其频率都为50kHz。SSC上升沿到来时标志着一次水平像素转移的结束和一次垂直行转移的开始,可通过控制四相A时钟信号的高低电平转换来完成。四相A时钟信号要满足严格的交迭原理,占空比为5:8,即五个单元的高电平和三个单元的低电平,所以相邻时钟信号之间的延迟为二个单元。A时钟信号的高电平有两个水平,分别用于CCD的不同工作状态,垂直转移状态的高电平要保持在14V,而光积分和保持状态高电平要保持在10V。TDA9991中集成了一个电平控制单元,可以完成对A时钟信号的电平控制。而在电平像素转换期间,A1必须继续保持低电平,A2、A3、A4保持高电平,从而保证光敏面中的未输出信号继续保持在A2、A3、A4电极之下。

3.2.3水平像素转移的驱动时序

该时序涉及C1、C2、C3、RG、SG,其频率都为25MHz。SSC下降沿到来时标志着一次垂直行转移的结束和一次水平像素转移的开始,转移原理和行转移原理一样,三相C时钟信号要严格满足三相交迭原理,占空比为3:6,也就是高低电平保持时间一样。在电荷由光敏区向输出寄存器转移的过程中(见图4),在SSC下降沿到来之前,C3应该保持低电平,使像素在输出寄存器的隔离开来,而C1和C2应该保持高电平,使转移下隔断的电荷在这两个电极之下积聚起来,为下一步的水平转移输出作准备。

4 实验与讨论

系统设计完成后,根据CCD的时序村注,经仿真调试可以产生出相应的驱动脉冲和偏置电压。但是由于系统的后续图像处理和传输部分还没有设计好,所以无法进行图像采集。该驱动电路的研制结果表明,采用现在芯片进行系统设计有它自身的好处,可以简化设计,而且调试简单、可扩展性也比较强。

电路 集成电路 单片机 电压 电流 DSP 传感器 放大器 电子 电容 总线 仿真 相关文章:

- TFT-LCD驱动电路的设计(08-27)

- 基于S3C2410的TFT-LCD驱动电路的设计(上)(09-03)

- 基于S3C2410的TFT-LCD驱动电路的设计(下)(09-03)

- 大势所趋的数字电源设计方式(11-04)

- 几种主流MOSFET驱动电路的分析(10-27)

- 前沿方案延缓LED老化(11-27)