基于S3C2410的TFT-LCD驱动电路的设计(下)

S3C2410 LCD控制器的设置方法

结构和信号说明

S3C2410 LCD控制器用来传输图像数据并产生相应的控制信号,该控制器由REGBANK(控制寄存器组)、LCDCDMA(专用DMA)、VIDPCS(视频信号处理单元)、LPC3600和TIMEGEN(时序信号产生单元)组成。其中REGBANK包含17个可编程寄存器和几个256×16的调色板存储器,用来配置LCD控制器,并设置相应的参数;而LCDCDMA提供了视频信号的快速传输通道,自动通过系统总线从系统帧缓存中取出视频数据,并传输到视频信号处理单元;VIDPCS将专用DMA中取出的信号进行整形并提高驱动能力等处理后,输出到外部数据端口VD[23:0]; TIMEGEN和LPC3600负责产生 LCD屏所需要的控制时序。

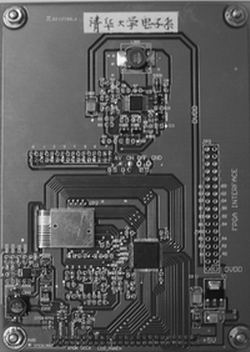

图6 液晶驱动电路底面图

S3C2410 LCD控制器可以产生的用于控制TFT-LCD的时序信号主要包括VCLK(像点时钟)、VDEN(数据有效信号)、VSYNC(垂直同步信号)、 HSYNC(水平同步信号)、LEND(行结束信号)及LCD_PWREN(液晶屏使能信号)。VCLK信号是LCD控制器和LCD驱动器的像素时钟信号, LCD控制器在VCLK信号的上升沿处将数据送出,在VCLK信号的下降沿处被LCD控制器采样;VSYNC信号是垂直同步信号(也称帧同步信号),用来指示新的一帧图像的开始;HSYNC信号是水平同步信号(或行同步信号),用来给出新的一行扫描信号的开始;VDEN信号是数据使能信号;LEND信号是行扫描结束信号,LCD驱动器在每扫描一行像素后给出该信号;LCD_PWREN信号用来控制LCD控制器的开或关,以便降低功耗,它需要LCD控制器硬件设计的支持。

寄存器和设置说明

S3C2410的LCD控制器内部设有较多的寄存器,其中与时序信号高度相关的寄存器位于寄存器组中的LCDCON1/2/3/4/5。本文设计的LCD 驱动器需要LCD控制器给出VCLK、VDEN、LCD_PWREN和VD[23:0]信号,其中VCLK信号依赖于LCDCON1寄存器中CLKVAL 和S3C2410的HCLK的取值,具体公式为:VCLK(Hz)=HCLK/[(CLKVAL+1)×2]。VSYNC和HSYNC的产生依赖于 LCDCON2/3寄存器及HOZVAL和LINEVAL的配置,其中HOZVAL=水平像素数-1,LINEVAL=垂直显示尺寸-1。帧频率 VSYNC与LCDCON1/2/3/4寄存器中的VSPW、VBPD、VFPD、LINEVAL、HSYNC、HBPD、HFPD、HOZVAL和 CLKVAL有关,具体公式为:

Frame Rate(VSYNC)=1/{[(VSPW+1)+(VBPD+1)+ (VFPD+1)+(LINEVAL+1)] ?(HSPW+1)+(HBPD+1)+ (HFPD+1)+(HOZVAL+1)] ?2?CLKVAL+1)/HVLK]}

其中,HOZVAL=240-1=239,LINEVAL=320-1=319。

系统测试结果

在软硬件研制开发完成后,对系统进行了测试,图6是PCB板的地面元件布局图,测试结果显示,液晶屏可以正常显示,该系统达到了设计要求。由于设计的硬件驱动电路只需要LCD 控制器给出像点时钟、数据使能信号和RGB数据信号,因此,为移植到不同的平台带来了较大的灵活性,实用性很强。

参考文献

1 Samsung Electronics. User’s Manual S3C2410X 32-Bit RISC Microprocessor [Z] .2003.372-413.

2 堀浩雄,铃木幸治主编,金轸裕译. 彩色液晶显示. 北京:科学出版社,2003

- TFT-LCD光阻回收再利用技术(08-20)

- 薄膜晶体管液晶显示器(TFT-LCD)(上)(08-20)

- 薄膜晶体管液晶显示器(TFT-LCD)(下)(08-20)

- TFT-LCD驱动电路的设计(08-27)

- 基于S3C2410的TFT-LCD驱动电路的设计(上)(09-03)

- 数码相机TFT-LCD的背光及亮度调整方式设计 (11-26)