高分辨率全帧CCD芯片FTF4027M的驱动电路设计

时间:09-11

来源:互联网

点击:

本文所要设计的驱动电路是机载CCD相机上的前端驱动电路。机载CCD相机能够将拍摄的图像以数字的形式采集、存储和传输,并与地面实现实时通信,因此可以很好地克服传统光学相机的缺点。随着CCD器件的快速发展,CCD驱动时序的产生有很多种方法,比如可以采用数字集成电路、单片机、EPROM器件或可编程逻辑器件等来实现。本文采用CCD专用的数字集成芯片和单片机进行设计来实现CCD驱动电路。它的优点是结构设计简单、设计周期短、电路可靠性强。而高速时序脉冲产生芯片的运用又克服了单片机晶振频率低的限制,因此足以满足高速大面阵CCD的驱动时序要求。

1 系统总体结构

CCD驱动电路系统框图如图1所示,它以微控制器P89LPC932作为系统总的控制单元,在其控制下,SAA8103与TDA9991共同为CCD芯片FTF4027M提供所需的驱动脉冲和偏置电压,协调整个相机同步工作。CCD输出的信号是带有固定图像噪声和暗电流的模拟信号,需要运用光学黑补偿箝位电路并通过相关双采样去除噪声干扰,然后进行可在控增益放大和模/数转换,这些工作由CCD专用的模拟处理芯片TDA9965来完成。输出的12位数字信号送给DSP以便进行进一步的数字图像处理。

2 FTF4027M的内部结构及驱动时序分析

FTF4027M是一款1100万像素(4008×2672)的超大分辨率全帧CCD图像传感器。其内部结构如图2所示。该款芯片在结构上分为三部分,中间最大的区域为光敏区,即光积分区域;上下两部分为两个输出寄存器,将光积分生成的电荷水平转移到四个角的输出放大器,输出放大器将光生电荷形成的电压信号放大并转移出CCD。该款芯片的最大特点是将光敏区生成的图像分成W、X、Y、Z四个对称的角限,每个象限的电荷可以以不同的方向转移,通过四个输出端同时输出,有效地增加了帧速率,单端输出的帧速率为2帧/秒,而四端同时输出就可以达到7.5帧/秒。在本应用中,单端输出就可以满足系统设计要求,因此采用单端输出方式,电荷转移方向如图中虚线所示,A1、A2、A3、A4为垂直驱动时钟信号,C1、C2、C3为水平移动时钟信号。

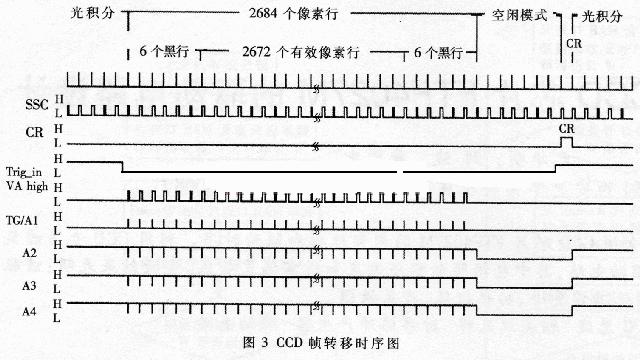

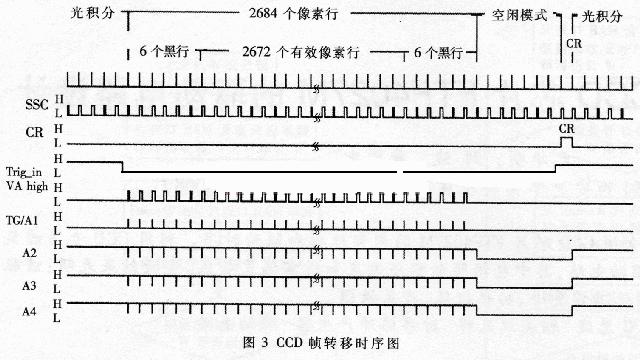

CCD的帧转移时序图如图3所示。SSC为系统内部基准时钟信号,用于校准整个CCD的时序;CR(Charge Reset)为CCD的电荷复位信号,相当于电子块门信号;Trig-in是CCD的外部触发信号,用于控制CCD光积分的起始和结束;VA-high是控制四相A时钟的高低电平转换的信号;TG是光敏区与输出寄存器之间的隔栅,TG信号的相位和频率与A1完全一致。整个帧时序分为三个阶段,这三个阶段是循环进行的。把空闲模式阶段定义为第一阶段,在CCD空闲模式下,A时钟信号全部保持低电平。空闲模式后,CCD开始进入第二阶段,即光积分阶段,A1继续保持低电平,A2、A3、A4上升为高电平。因为CCD中的每个像素都可以看作是由四个栅极(每个栅极上连接一相时钟信号)“覆盖”的,而且像素之间必须分离开,水平方向上可以通过沟道隔离像素。为了将像素与像素在垂直方向上隔离开,必须将四个栅极中的某一个栅极电压变为0。

在本应用中,将A1保持低电平以起到像素隔离的作用而光生电荷则在保持高电平的A2、A3、A4的栅极下积聚起来,形成信号电荷包。光积分结束后进入第三阶段,即帧转移阶段,而帧转移又可以看成是垂直行转移和水平像素转移交替进行的,它们之间的交换转换是通过SSC电平的高低转换实现的。在SSC保持高电平时,光敏区里已经生成的光电荷在四相A时钟信号的驱动下逐行地向下转移到输出寄存器的。如图4所示,每转移完一行,SSC变为低电平,则输出寄存器就在三相C时钟信号的驱动下将这一行逐个像素地向输出放大器转移。输出放大器内有一个浮置扩散电容FD(Floating Diffusion Capacitance),它可以将接收到的电荷包转换为电压信号。

RG(Reset Gate)是通过复位管对FD进行复位的信号,复位后FD可以接收下一个电荷包。SG(Summing Gate)是在输出栅OG之前的最后一个栅,SG信号和RG信号的相位与C3信号的相位相同。一行电荷包经过输出放大器的转换和放大后以电压信号的形式从CCD输出,接下来再进行下一行的垂直行转移和水平像素转移输出,直到光敏面上的所有2684行电荷包输出完毕为止。由此可见,整个一帧图像是在A时钟信号和C时钟信号的交替驱动下从CCD输出而完成帧转移的。

3 系统设计

由于本系统中采用的芯片都是CCD专用的芯片,因此硬件电路设计相对简单一些,主要工作是软件设计。本系统内部的微控制单元为P89LPC932型单片机,它是一款高性能、低功耗、高速度的小封装微控制器,内带I2C控制器。SAA8103也是一个I2C器件,内部有一个寄存器,专门用来保存设定的CCD驱动脉冲和偏置电压的工作参数烧写到单片机的Flash程序存储器中,然后将这些参数在系统上电后通过I2C总线传输到SAA8103的寄存器内,再通过三线串行总线为TDA9965和TDA9991进行设定和控制,从而让CCD在最佳的状态下与后续图像处理和图像传输单元协调工作。

1 系统总体结构

CCD驱动电路系统框图如图1所示,它以微控制器P89LPC932作为系统总的控制单元,在其控制下,SAA8103与TDA9991共同为CCD芯片FTF4027M提供所需的驱动脉冲和偏置电压,协调整个相机同步工作。CCD输出的信号是带有固定图像噪声和暗电流的模拟信号,需要运用光学黑补偿箝位电路并通过相关双采样去除噪声干扰,然后进行可在控增益放大和模/数转换,这些工作由CCD专用的模拟处理芯片TDA9965来完成。输出的12位数字信号送给DSP以便进行进一步的数字图像处理。

2 FTF4027M的内部结构及驱动时序分析

FTF4027M是一款1100万像素(4008×2672)的超大分辨率全帧CCD图像传感器。其内部结构如图2所示。该款芯片在结构上分为三部分,中间最大的区域为光敏区,即光积分区域;上下两部分为两个输出寄存器,将光积分生成的电荷水平转移到四个角的输出放大器,输出放大器将光生电荷形成的电压信号放大并转移出CCD。该款芯片的最大特点是将光敏区生成的图像分成W、X、Y、Z四个对称的角限,每个象限的电荷可以以不同的方向转移,通过四个输出端同时输出,有效地增加了帧速率,单端输出的帧速率为2帧/秒,而四端同时输出就可以达到7.5帧/秒。在本应用中,单端输出就可以满足系统设计要求,因此采用单端输出方式,电荷转移方向如图中虚线所示,A1、A2、A3、A4为垂直驱动时钟信号,C1、C2、C3为水平移动时钟信号。

CCD的帧转移时序图如图3所示。SSC为系统内部基准时钟信号,用于校准整个CCD的时序;CR(Charge Reset)为CCD的电荷复位信号,相当于电子块门信号;Trig-in是CCD的外部触发信号,用于控制CCD光积分的起始和结束;VA-high是控制四相A时钟的高低电平转换的信号;TG是光敏区与输出寄存器之间的隔栅,TG信号的相位和频率与A1完全一致。整个帧时序分为三个阶段,这三个阶段是循环进行的。把空闲模式阶段定义为第一阶段,在CCD空闲模式下,A时钟信号全部保持低电平。空闲模式后,CCD开始进入第二阶段,即光积分阶段,A1继续保持低电平,A2、A3、A4上升为高电平。因为CCD中的每个像素都可以看作是由四个栅极(每个栅极上连接一相时钟信号)“覆盖”的,而且像素之间必须分离开,水平方向上可以通过沟道隔离像素。为了将像素与像素在垂直方向上隔离开,必须将四个栅极中的某一个栅极电压变为0。

在本应用中,将A1保持低电平以起到像素隔离的作用而光生电荷则在保持高电平的A2、A3、A4的栅极下积聚起来,形成信号电荷包。光积分结束后进入第三阶段,即帧转移阶段,而帧转移又可以看成是垂直行转移和水平像素转移交替进行的,它们之间的交换转换是通过SSC电平的高低转换实现的。在SSC保持高电平时,光敏区里已经生成的光电荷在四相A时钟信号的驱动下逐行地向下转移到输出寄存器的。如图4所示,每转移完一行,SSC变为低电平,则输出寄存器就在三相C时钟信号的驱动下将这一行逐个像素地向输出放大器转移。输出放大器内有一个浮置扩散电容FD(Floating Diffusion Capacitance),它可以将接收到的电荷包转换为电压信号。

RG(Reset Gate)是通过复位管对FD进行复位的信号,复位后FD可以接收下一个电荷包。SG(Summing Gate)是在输出栅OG之前的最后一个栅,SG信号和RG信号的相位与C3信号的相位相同。一行电荷包经过输出放大器的转换和放大后以电压信号的形式从CCD输出,接下来再进行下一行的垂直行转移和水平像素转移输出,直到光敏面上的所有2684行电荷包输出完毕为止。由此可见,整个一帧图像是在A时钟信号和C时钟信号的交替驱动下从CCD输出而完成帧转移的。

3 系统设计

由于本系统中采用的芯片都是CCD专用的芯片,因此硬件电路设计相对简单一些,主要工作是软件设计。本系统内部的微控制单元为P89LPC932型单片机,它是一款高性能、低功耗、高速度的小封装微控制器,内带I2C控制器。SAA8103也是一个I2C器件,内部有一个寄存器,专门用来保存设定的CCD驱动脉冲和偏置电压的工作参数烧写到单片机的Flash程序存储器中,然后将这些参数在系统上电后通过I2C总线传输到SAA8103的寄存器内,再通过三线串行总线为TDA9965和TDA9991进行设定和控制,从而让CCD在最佳的状态下与后续图像处理和图像传输单元协调工作。

电路 集成电路 单片机 电压 电流 DSP 传感器 放大器 电子 电容 总线 仿真 相关文章:

- TFT-LCD驱动电路的设计(08-27)

- 基于S3C2410的TFT-LCD驱动电路的设计(上)(09-03)

- 基于S3C2410的TFT-LCD驱动电路的设计(下)(09-03)

- 大势所趋的数字电源设计方式(11-04)

- 几种主流MOSFET驱动电路的分析(10-27)

- 前沿方案延缓LED老化(11-27)