USB2.0虚拟逻辑分析仪的设计与实现

时间:09-15

来源:互联网

点击:

USB2.0接口设计

本设计选用符合USB2.0规范的CP2102芯片构建系统与PC的通信接口。

CP2102是USB-UART桥接芯片。该电路内置USB2.0全速功能控制器、USB收发器、晶体振荡器、EEPROM及异步串行数据总线,支持调制解调器全功能信号,无需任何外部的USB器件。其功能强大,采用MLP-28封装,尺寸仅为5mm×5mm,占用空间非常小,非常适合大数据量处理与传输电路系统的设计与应用。

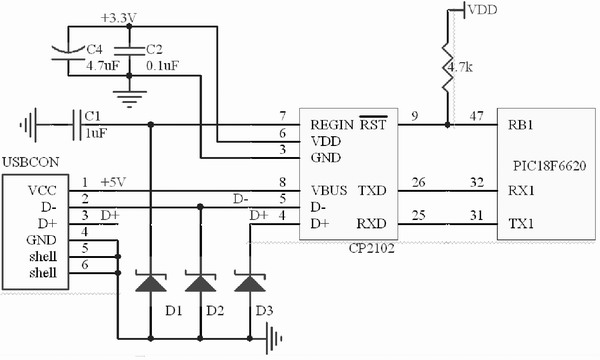

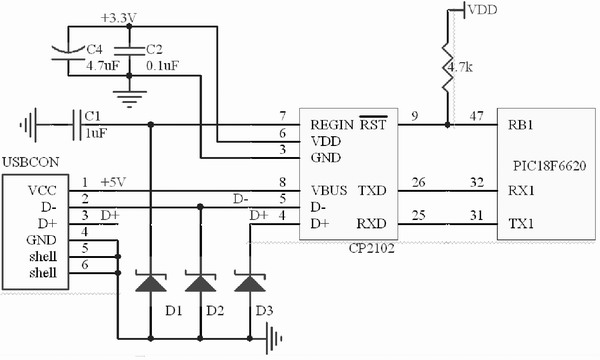

实际应用中,系统只需使用CP2102基本的输入/输出数据线与复位信号线。其接口原理如图2所示。

图2 USB2.0接口电路图

系统启动时, 单片机RB1端口发送一低电平至CP2102复位端,芯片复位,然后保持复位端高电平,CP2102正常工作。

由于CP2102内部的透明设计,数据通信时,可以不必构建CP2102与单片机的握手信号;CP2102数据线直接与单片机1#USART模块的接收移位寄存器(RSR)和发送移位寄存器(TSR)相连。CP2102数据线上一旦出现待发送的数据,该数据会自动移入单片机接收移位寄存器;同样,单片机发送数据时,发送移位寄存器中的数据直接移至CP2102的数据线(即USB接口数据线)上。

程序设计中,系统不断检测单片机接收中断标志位RCIF1,一旦USART异步接收器的移位寄存器RSR接收到CP2102数据线上发送的停止位,RSR寄存器就将已接收的8位数据装载到接收寄存器(RCREG1)中。系统发送数据时,前次装入发送缓冲器(TXREG1)的数据的停止位P发送出去后,TXREG1缓冲器中的数据(软件装入)就被载入TSR寄存器中,TXREG1缓冲器就为空状态,同时发送中断标志位TXIF被置1。TSR将待发送数据逐位移至CP2102数据线,完成系统与CP2102 USB模块的数据传输。

软件设计

FPGA功能实现程序运用硬件描述语言Verilog HDL编写;PIC单片机程序用C语言编写,并采用第三方C语言工具HITECH公司PICC—18编译器编译实现。PC显示和操作部分运用图形化语言LabView7.1编写,其前面板如图3所示。

图3 系统面板

实验操作

采用LabView7.1开发的虚拟操作平台,可以方便实现仪器的操作控制。实验开始前,首先选择通信端口,建立PC与本系统的通信;设置触发电平,设置采样频率(外部、内部或其他)、触发方式、触发字、屏蔽字并点击“发送触发命令”按钮,完成相关设置,开启数据采集和触发进程。点击“读取采样数据”可读出采集到的数据,并在PC上显示。

结语

在综合考虑应用需要和成本的前提下,本设计采用4个高速采样通道,最高可达75MHz采样率,存储深度达512KB,最多可采集220个测试点。触发电平由10位串行数模转换器TLC5615产生,电平误差小于5mV。高速USB2.0通信接口配合LabView7.1开发的虚拟操作平台,可实现数据在PC上的实时显示。本设计的成本还不到市场上同性能产品的1/2,更适用于教学等对产品数量要求较多,性能要求中等的单位采用。

本设计选用符合USB2.0规范的CP2102芯片构建系统与PC的通信接口。

CP2102是USB-UART桥接芯片。该电路内置USB2.0全速功能控制器、USB收发器、晶体振荡器、EEPROM及异步串行数据总线,支持调制解调器全功能信号,无需任何外部的USB器件。其功能强大,采用MLP-28封装,尺寸仅为5mm×5mm,占用空间非常小,非常适合大数据量处理与传输电路系统的设计与应用。

实际应用中,系统只需使用CP2102基本的输入/输出数据线与复位信号线。其接口原理如图2所示。

图2 USB2.0接口电路图

系统启动时, 单片机RB1端口发送一低电平至CP2102复位端,芯片复位,然后保持复位端高电平,CP2102正常工作。

由于CP2102内部的透明设计,数据通信时,可以不必构建CP2102与单片机的握手信号;CP2102数据线直接与单片机1#USART模块的接收移位寄存器(RSR)和发送移位寄存器(TSR)相连。CP2102数据线上一旦出现待发送的数据,该数据会自动移入单片机接收移位寄存器;同样,单片机发送数据时,发送移位寄存器中的数据直接移至CP2102的数据线(即USB接口数据线)上。

程序设计中,系统不断检测单片机接收中断标志位RCIF1,一旦USART异步接收器的移位寄存器RSR接收到CP2102数据线上发送的停止位,RSR寄存器就将已接收的8位数据装载到接收寄存器(RCREG1)中。系统发送数据时,前次装入发送缓冲器(TXREG1)的数据的停止位P发送出去后,TXREG1缓冲器中的数据(软件装入)就被载入TSR寄存器中,TXREG1缓冲器就为空状态,同时发送中断标志位TXIF被置1。TSR将待发送数据逐位移至CP2102数据线,完成系统与CP2102 USB模块的数据传输。

软件设计

FPGA功能实现程序运用硬件描述语言Verilog HDL编写;PIC单片机程序用C语言编写,并采用第三方C语言工具HITECH公司PICC—18编译器编译实现。PC显示和操作部分运用图形化语言LabView7.1编写,其前面板如图3所示。

图3 系统面板

实验操作

采用LabView7.1开发的虚拟操作平台,可以方便实现仪器的操作控制。实验开始前,首先选择通信端口,建立PC与本系统的通信;设置触发电平,设置采样频率(外部、内部或其他)、触发方式、触发字、屏蔽字并点击“发送触发命令”按钮,完成相关设置,开启数据采集和触发进程。点击“读取采样数据”可读出采集到的数据,并在PC上显示。

结语

在综合考虑应用需要和成本的前提下,本设计采用4个高速采样通道,最高可达75MHz采样率,存储深度达512KB,最多可采集220个测试点。触发电平由10位串行数模转换器TLC5615产生,电平误差小于5mV。高速USB2.0通信接口配合LabView7.1开发的虚拟操作平台,可实现数据在PC上的实时显示。本设计的成本还不到市场上同性能产品的1/2,更适用于教学等对产品数量要求较多,性能要求中等的单位采用。

FPGA Altera PIC 单片机 USB DAC 电压 比较器 电路 PWM Verilog 收发器 振荡器 总线 电路图 C语言 相关文章:

- 远程测控中嵌入式Web服务器的FPGA实现(10-30)

- 基于DSP Builder的DDS设计及其FPGA实现(11-03)

- 基于FPGA的DDS调频信号的研究与实现 (11-04)

- 使用混合信号示波器验证测量混合信号电路(11-05)

- 基于速度匹配软件的网络芯片仿真方法(11-06)

- 利用FPGA实现原型板原理图的验证(11-07)