用于SOC或块级时钟的可配置分频器

时间:12-06

来源:互联网

点击:

FCD的概念

举一个分数时钟分频的例子,就可以理解FCD的概念。

假设时钟分频为1.3 - 这样时钟的最小频率fmin= 1.5,最大频率fmax= 1

也就是说:输出时钟的10个周期=输入时钟的13个周期

设最小频率的输出时钟周期数为X

设最大频率的输出时钟周期数为Y

因此

x + y = 10

1.5 x + Y = 13

由此我们解出

x = 6 y =4

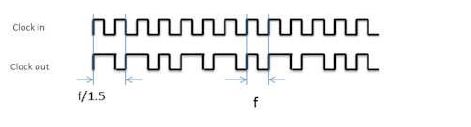

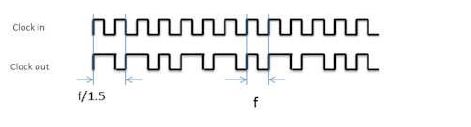

这样,6×1.5=9个输入时钟周期,将除以1.5, 4个输入时钟周期将除以1。 1.3分频的波形图如下所示。这些分频器常常用于逐级时钟频率切换,防止在瞬间出现高电流消耗(这可能导致晶体管的Vdd口出现异常电压下降或上升,破坏设计,并可能引起芯片复位)。时钟频率的步长随着设计中每单位时间允许的最大频率增加或减少。

图9:分数时钟分频。

本文结论

本文向人们展示了目前大多数设计中都使用的基本可配置时钟分频器。尽管实施方案可能会有所不同,但是可配置分频器的基本思路是一致的。由于每种时钟分频器各有优点和局限性,设计人员在选择时钟分频器类型时需要格外注意。虽然穿通时钟方案使DFT时钟更加简单,其占空比局限性给时序团队在分频时钟域关闭关键的半周期路径时留下了繁琐的工作。基于多路选择器的分频器提供50%占空比的输出时钟,但可能使DFT时钟变得复杂。因此,如果在设计早期,从功能,DFT和时序方面详细了解和分析时钟的关键性因素,避免时钟架构变化,可能会在之后的时序收敛阶段带来意想不到的惊喜。

关于作者

Prateek Gupta作为飞思卡尔半导体公司的设计工程师已经有2年多工作经验,在物理设计团队中,他专攻静态时序分析。他负责90nm和55nm技术的多个设计模块的时序收敛和ECO实施。

Priyanka Garg在飞思卡尔半导体公司担任了一年多的设计工程师。目前,她在布局和布线团队工作。她曾致力于分层和平面SOC设计。此外,她还成功制定了55和40 nm技术的各种时钟树合成战略。

举一个分数时钟分频的例子,就可以理解FCD的概念。

假设时钟分频为1.3 - 这样时钟的最小频率fmin= 1.5,最大频率fmax= 1

也就是说:输出时钟的10个周期=输入时钟的13个周期

设最小频率的输出时钟周期数为X

设最大频率的输出时钟周期数为Y

因此

x + y = 10

1.5 x + Y = 13

由此我们解出

x = 6 y =4

这样,6×1.5=9个输入时钟周期,将除以1.5, 4个输入时钟周期将除以1。 1.3分频的波形图如下所示。这些分频器常常用于逐级时钟频率切换,防止在瞬间出现高电流消耗(这可能导致晶体管的Vdd口出现异常电压下降或上升,破坏设计,并可能引起芯片复位)。时钟频率的步长随着设计中每单位时间允许的最大频率增加或减少。

图9:分数时钟分频。

本文结论

本文向人们展示了目前大多数设计中都使用的基本可配置时钟分频器。尽管实施方案可能会有所不同,但是可配置分频器的基本思路是一致的。由于每种时钟分频器各有优点和局限性,设计人员在选择时钟分频器类型时需要格外注意。虽然穿通时钟方案使DFT时钟更加简单,其占空比局限性给时序团队在分频时钟域关闭关键的半周期路径时留下了繁琐的工作。基于多路选择器的分频器提供50%占空比的输出时钟,但可能使DFT时钟变得复杂。因此,如果在设计早期,从功能,DFT和时序方面详细了解和分析时钟的关键性因素,避免时钟架构变化,可能会在之后的时序收敛阶段带来意想不到的惊喜。

关于作者

Prateek Gupta作为飞思卡尔半导体公司的设计工程师已经有2年多工作经验,在物理设计团队中,他专攻静态时序分析。他负责90nm和55nm技术的多个设计模块的时序收敛和ECO实施。

Priyanka Garg在飞思卡尔半导体公司担任了一年多的设计工程师。目前,她在布局和布线团队工作。她曾致力于分层和平面SOC设计。此外,她还成功制定了55和40 nm技术的各种时钟树合成战略。

飞思卡尔 半导体 电路 振荡器 SoC 电流 电压 相关文章:

- 飞思卡尔TSSMCU: 面向微控制器的Xtrinsic触摸传感(02-22)

- 飞思卡尔Xtrinsic MPL3115A2智能压力传感器(02-22)

- 飞思卡尔MMA955xL: Xtrinsic运动感应平台(02-22)

- 探究现代数字调制技术(04-09)

- 基于MHVIC2115的射频功率放大器设计(12-02)

- 飞思卡尔汽车远程无钥匙进入系统方案和VKSP安全协(08-18)