基于Blackfin561的JPEG2000压缩算法实现及优化

时间:11-28

来源:互联网

点击:

1 引言

JPEG2000数字图像压缩标准是国际标准组织(ISO)和国际电信联盟(ITU)联合制定的新一代静止图像压缩标准。与以往的压缩标准相比,JPEG2000标准具有很多优点。它不仅仅在图像编码过程中能保证良好的图像质量,而且还具有现代图像压缩所要求的新性能,如同时支持有损压缩和无损压缩两种模式、保证在图像传输过程中的容错性、支持感兴趣区域编码等。但是,由于新技术的引入,JPEG2000的算法复杂度也相应提高,在实际应用中,JPEG2000并不如想象中的那么应用广泛。而DSP由于其丰富灵活的指令集、特殊的内部结构、超强的数据吞吐能力及运算速度,使得以DSP处理器为核心的方法成为实现JPEG2000算法的一种有效途径。

2 JPEG2000系统的组成原理

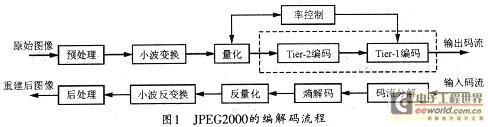

JPEG2000相对于JPEG的最大改进就是以离散小波变换(DWT)代替了DCT编码。JPEG2000的编解码流程如图1所示。本系统首先对源图像数据进行离散小波变换,然后对变换后的小波系数进行量化,接着对量化后的数据熵编码,最后形成输出码流。解码器是编码器的逆过程,解码时,首先对码流进行熵解码,然后解量化和小波反变换,最后生成重建图像数据。

通过预处理可为不同类型的图像提供一个统一的接口,以便于后续使用同样的编码器进行处理,这一步骤是将多种类型的图像压缩加入到统一框架中的关键。它主要包括三个步骤:图像分片、直流平移和分量变换。

小波的多分辨率分析特性使之既可高效地描述图像的平坦区域,又可有效地表示图像信号的局部突变(即图像的边缘轮廓部分),它在空域和频域都有良好的局部性,因而能够聚焦到图像的任意细节。

优化截断嵌入块编码(The Embedded BlockCoding with Optimized Truncation,简称EBCOT)是JPEG2000标准的核心,它不仅能对图像进行有效压缩,同时,其产生的码流还具有分辨率可伸缩性、信噪比可伸缩性、随机访问和处理等非常好的特性。EBCOT分Tierl和Tier2两部分,EBCOT可将子带分成互不重叠的编码块,每个编码块的比特层编码称为Tierl;然后对所有编码块的编码流进行优化截断排序和打包等处理,以使其成为Tier2。

3 Blackfin56l处理器

Blackfin处理器是一类专为满足当今嵌入式音频、视频和通信应用的计算要求和功耗约束条件而设计的新型32位DSP。Blackfin处理器主要基于ADI和Intel公司联合开发的微信号架构(MSA),它将一个32位RISC型指令集和双16位乘法累加(MAC)信号处理功能与通用型微控制器所具有的易用性组合在了一起。Blackfin561是Blackfin处理器系列中的新型对称双核处理器成员,可在相同的频率条件下实现性能的翻番。该器件具有以下特点:

(1)高性能的处理器内核

Blackfin处理器架构基于一个10级RISCMCU/DSP流水线和一个专为实现最佳代码密度而设计的混合16/32位指令集架构。Blackfin561具有两个内核频率可达600MHz的处理器,可提供高效RISC MCU控制任务执行能力。

(2)高带宽DMA能力

Blackfin561具有多个独立的DMA控制器,这些控制器可支持自动数据传输,而且所需的处理器内核开销极少。DMA传输可出现于内部存储器和诸多具有DMA功能的外设之间。传输也有可能出现于外设和与外部存储器接口相连的外部器件之间,包括SDRAM控制器和异步存储器控制器。

(3)专用视频指令

除了具有对8位数据以及许多像素处理算法所常用的字长的固有支持之外,Blackfin处理器架构还包括专为增强视频处理应用而定义的指令。

(4)高效控制处理

Blackfin561提供有各种各样的微控制器型外设,包括UARTS、SPI、PPI控制器、支持PWM的定时器、看门狗定时器、实时时钟和一个无缝同步和异步存储器控制器。因而为设计师提供了巨大的设计灵活性,并最大限度地降低了终端系统成本。

(5)分层的存储器架构

Blackfin561支持改进的哈佛结构,该结构是具有分级的存储器结构的组合。BF56l器件的地址总线宽度为32位,可以访问4G字节的地址空间。Blackfin处理器的存储器架构在器件实现中可提供Level l(L1)和Level 2(L2)存储模块,并可以通过EBIU外接L3处理器(SDRAM、Flash等)。

4 系统设计

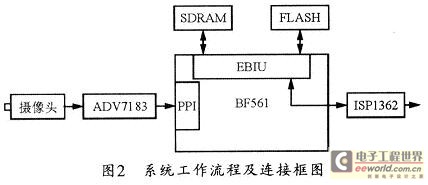

本系统主要实现数字图像的采集和压缩处理。它有效利用了Blackfin561的专用视频接口PPI和其它丰富的接口资源,具有设计简单、便于软件编程的特点。图2所示其系统工作流程及连接框图。

由图2可见,本系统首先由CCD摄像头来采集图像,输入的模拟信号经ADV7183视频编码芯片转换成ITU一656格式的数字视频流,该视频流通过BF561的PPI传输到SDRAM。然后由DSP从SDRAM读入图像,并执行JPEG2000编码操作,最后将压缩视频流输入到输出模块进行传输。输出模块由USB控制芯片ISPl362组成,可以实现系统和PC机的互连。FLASH用来存放加载文件LDR。

JPEG2000数字图像压缩标准是国际标准组织(ISO)和国际电信联盟(ITU)联合制定的新一代静止图像压缩标准。与以往的压缩标准相比,JPEG2000标准具有很多优点。它不仅仅在图像编码过程中能保证良好的图像质量,而且还具有现代图像压缩所要求的新性能,如同时支持有损压缩和无损压缩两种模式、保证在图像传输过程中的容错性、支持感兴趣区域编码等。但是,由于新技术的引入,JPEG2000的算法复杂度也相应提高,在实际应用中,JPEG2000并不如想象中的那么应用广泛。而DSP由于其丰富灵活的指令集、特殊的内部结构、超强的数据吞吐能力及运算速度,使得以DSP处理器为核心的方法成为实现JPEG2000算法的一种有效途径。

2 JPEG2000系统的组成原理

JPEG2000相对于JPEG的最大改进就是以离散小波变换(DWT)代替了DCT编码。JPEG2000的编解码流程如图1所示。本系统首先对源图像数据进行离散小波变换,然后对变换后的小波系数进行量化,接着对量化后的数据熵编码,最后形成输出码流。解码器是编码器的逆过程,解码时,首先对码流进行熵解码,然后解量化和小波反变换,最后生成重建图像数据。

通过预处理可为不同类型的图像提供一个统一的接口,以便于后续使用同样的编码器进行处理,这一步骤是将多种类型的图像压缩加入到统一框架中的关键。它主要包括三个步骤:图像分片、直流平移和分量变换。

小波的多分辨率分析特性使之既可高效地描述图像的平坦区域,又可有效地表示图像信号的局部突变(即图像的边缘轮廓部分),它在空域和频域都有良好的局部性,因而能够聚焦到图像的任意细节。

优化截断嵌入块编码(The Embedded BlockCoding with Optimized Truncation,简称EBCOT)是JPEG2000标准的核心,它不仅能对图像进行有效压缩,同时,其产生的码流还具有分辨率可伸缩性、信噪比可伸缩性、随机访问和处理等非常好的特性。EBCOT分Tierl和Tier2两部分,EBCOT可将子带分成互不重叠的编码块,每个编码块的比特层编码称为Tierl;然后对所有编码块的编码流进行优化截断排序和打包等处理,以使其成为Tier2。

3 Blackfin56l处理器

Blackfin处理器是一类专为满足当今嵌入式音频、视频和通信应用的计算要求和功耗约束条件而设计的新型32位DSP。Blackfin处理器主要基于ADI和Intel公司联合开发的微信号架构(MSA),它将一个32位RISC型指令集和双16位乘法累加(MAC)信号处理功能与通用型微控制器所具有的易用性组合在了一起。Blackfin561是Blackfin处理器系列中的新型对称双核处理器成员,可在相同的频率条件下实现性能的翻番。该器件具有以下特点:

(1)高性能的处理器内核

Blackfin处理器架构基于一个10级RISCMCU/DSP流水线和一个专为实现最佳代码密度而设计的混合16/32位指令集架构。Blackfin561具有两个内核频率可达600MHz的处理器,可提供高效RISC MCU控制任务执行能力。

(2)高带宽DMA能力

Blackfin561具有多个独立的DMA控制器,这些控制器可支持自动数据传输,而且所需的处理器内核开销极少。DMA传输可出现于内部存储器和诸多具有DMA功能的外设之间。传输也有可能出现于外设和与外部存储器接口相连的外部器件之间,包括SDRAM控制器和异步存储器控制器。

(3)专用视频指令

除了具有对8位数据以及许多像素处理算法所常用的字长的固有支持之外,Blackfin处理器架构还包括专为增强视频处理应用而定义的指令。

(4)高效控制处理

Blackfin561提供有各种各样的微控制器型外设,包括UARTS、SPI、PPI控制器、支持PWM的定时器、看门狗定时器、实时时钟和一个无缝同步和异步存储器控制器。因而为设计师提供了巨大的设计灵活性,并最大限度地降低了终端系统成本。

(5)分层的存储器架构

Blackfin561支持改进的哈佛结构,该结构是具有分级的存储器结构的组合。BF56l器件的地址总线宽度为32位,可以访问4G字节的地址空间。Blackfin处理器的存储器架构在器件实现中可提供Level l(L1)和Level 2(L2)存储模块,并可以通过EBIU外接L3处理器(SDRAM、Flash等)。

4 系统设计

本系统主要实现数字图像的采集和压缩处理。它有效利用了Blackfin561的专用视频接口PPI和其它丰富的接口资源,具有设计简单、便于软件编程的特点。图2所示其系统工作流程及连接框图。

由图2可见,本系统首先由CCD摄像头来采集图像,输入的模拟信号经ADV7183视频编码芯片转换成ITU一656格式的数字视频流,该视频流通过BF561的PPI传输到SDRAM。然后由DSP从SDRAM读入图像,并执行JPEG2000编码操作,最后将压缩视频流输入到输出模块进行传输。输出模块由USB控制芯片ISPl362组成,可以实现系统和PC机的互连。FLASH用来存放加载文件LDR。

DSP 解码器 编码器 嵌入式 ADI MCU PWM 看门狗 总线 USB C语言 仿真 相关文章:

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)