MAX1148型高精度14位串行A/D转换器

时间:09-18

来源:互联网

点击:

3.3 A/D转换过程

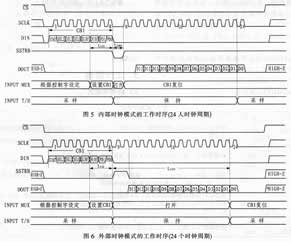

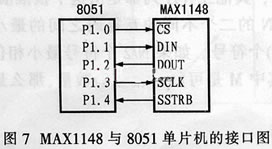

MAXll48在时钟脉冲的作用下进行逐次逼近式A/D转换,一般每24个时钟周期完成一次转换和读出操作。内部时钟模式与外部时钟模式的时序如图5、图6所示。

A/D转换速度要求不是很高时,常选用内部时钟模式。现以内部时钟模式为例说明MAXll48的工作过程:

首先根据系统要求确定MAXll48的控制字,例如,需转换0通道的单端单极性模拟量,控制字为8EH。然后向MAXll48输入控制字并读取转换结果,其步骤为:

(1)使片选端CS变为低电平并保持不变,此时DOUT处于低电平,SSTRB处于高电平;

(2)在DIN输入端由高到低依次输入控制字各位的值。

具体做法是:首先使DIN端为高电平(输入“l”),在第一个SCLK的上升沿将DIN的第一位数据“l”移入内部移位寄存器中。即移入START开始位:以此类推,在后面7个SCIJK的上升沿分别将输入DIN端的控制字其他位移入内部移位寄存器中;

(3)当控制字的最后一位数据被移入之后(第8个SCLK的下降沿),转换开始,SSTRB由高变低;

(4)经tcoNv之后,A/D转换结束,SSTRB由低变高。

(5)在转换结束后的任何时刻,通过SCLK时钟将移位寄存器中的转换结果(14位二进制数)由DOUT端同步移出。具体做法是:从SSTRB置高后的第二个SCLK时钟的下降沿开始,利用SCLK时钟逐一将转换后的结果从DOUT端移出,最高有效位在前。

4 MAXll48的应用举例

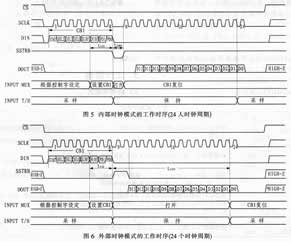

MAXll48通过DIN、DOUT、SCLK、SSTRB和CS5个信号与微处理器连接,其中,SSTRB是反映ADC转换状态的标志.可以用查询方式和中断方式监视此信号,以决定何时读取转换结果。如果是外部时钟模式或内部时钟模式中的软件延时,此信号可以空置不用。MAXll48与8位微处理器的典型连接如图7所示。

下面给出内部时钟模式下完整的转换和控制程序(转换结果在30H和31H中),以供参考:

START:CLR P1-3 :SCLK为低电平

CLR P1.0 :片选有效

MOV A,#lXXXXXl0B :控制字送A

MOV R1,#08H :输入控制字位数

LPl:MOV C,ACC.7 :取控制字并送至DIN端口

MOV P1.1,C

SETB P1.3 ;DIN端口数据移入内部移

位寄存器

CLR P1.3

RL A :控制字移位

DJNZ R1,LPl

LP2:JNB P1.4,LP2 ;检测SSTRB,等待转换结束

SETB P1.3

CLR P1.3

CLR A

MOV R1,#06H ;读入高6位数据

LP3:RL A

SETB P1.3

CLR P1.3

MOV C,P1.2

MOV ACC.0,C

DJNZ R1,LP3

MOV 30H,A

MOV R1,#08H ;读入低8位数据

LP4:RL A

SETB P1.3

CLR P1.3

MOV C,P1.2

MOV ACC.0,C

DJNZ R1,LP4

MOV 31H,A

STAY:SJMP STAY

END

外部时钟模式编程与内部时钟模式基本相似, 只需把控制字改为#1XXXXXllB,并删除上述程序中标号为U)2的程序行即可。

5 结束语

随着电子技术的不断发展,各种串行接口电路的应用越来越多.如串行A/D、D/A及各种接口电路等。与一般ADC器件相比,MAXll48具有单电源供电、自带内部基准电压、转换精度高、外围电路简单、占用微处理器口线少、易于连接等优点,适用于较复杂的测控系统。

MAXll48在时钟脉冲的作用下进行逐次逼近式A/D转换,一般每24个时钟周期完成一次转换和读出操作。内部时钟模式与外部时钟模式的时序如图5、图6所示。

A/D转换速度要求不是很高时,常选用内部时钟模式。现以内部时钟模式为例说明MAXll48的工作过程:

首先根据系统要求确定MAXll48的控制字,例如,需转换0通道的单端单极性模拟量,控制字为8EH。然后向MAXll48输入控制字并读取转换结果,其步骤为:

(1)使片选端CS变为低电平并保持不变,此时DOUT处于低电平,SSTRB处于高电平;

(2)在DIN输入端由高到低依次输入控制字各位的值。

具体做法是:首先使DIN端为高电平(输入“l”),在第一个SCLK的上升沿将DIN的第一位数据“l”移入内部移位寄存器中。即移入START开始位:以此类推,在后面7个SCIJK的上升沿分别将输入DIN端的控制字其他位移入内部移位寄存器中;

(3)当控制字的最后一位数据被移入之后(第8个SCLK的下降沿),转换开始,SSTRB由高变低;

(4)经tcoNv之后,A/D转换结束,SSTRB由低变高。

(5)在转换结束后的任何时刻,通过SCLK时钟将移位寄存器中的转换结果(14位二进制数)由DOUT端同步移出。具体做法是:从SSTRB置高后的第二个SCLK时钟的下降沿开始,利用SCLK时钟逐一将转换后的结果从DOUT端移出,最高有效位在前。

4 MAXll48的应用举例

MAXll48通过DIN、DOUT、SCLK、SSTRB和CS5个信号与微处理器连接,其中,SSTRB是反映ADC转换状态的标志.可以用查询方式和中断方式监视此信号,以决定何时读取转换结果。如果是外部时钟模式或内部时钟模式中的软件延时,此信号可以空置不用。MAXll48与8位微处理器的典型连接如图7所示。

下面给出内部时钟模式下完整的转换和控制程序(转换结果在30H和31H中),以供参考:

START:CLR P1-3 :SCLK为低电平

CLR P1.0 :片选有效

MOV A,#lXXXXXl0B :控制字送A

MOV R1,#08H :输入控制字位数

LPl:MOV C,ACC.7 :取控制字并送至DIN端口

MOV P1.1,C

SETB P1.3 ;DIN端口数据移入内部移

位寄存器

CLR P1.3

RL A :控制字移位

DJNZ R1,LPl

LP2:JNB P1.4,LP2 ;检测SSTRB,等待转换结束

SETB P1.3

CLR P1.3

CLR A

MOV R1,#06H ;读入高6位数据

LP3:RL A

SETB P1.3

CLR P1.3

MOV C,P1.2

MOV ACC.0,C

DJNZ R1,LP3

MOV 30H,A

MOV R1,#08H ;读入低8位数据

LP4:RL A

SETB P1.3

CLR P1.3

MOV C,P1.2

MOV ACC.0,C

DJNZ R1,LP4

MOV 31H,A

STAY:SJMP STAY

END

外部时钟模式编程与内部时钟模式基本相似, 只需把控制字改为#1XXXXXllB,并删除上述程序中标号为U)2的程序行即可。

5 结束语

随着电子技术的不断发展,各种串行接口电路的应用越来越多.如串行A/D、D/A及各种接口电路等。与一般ADC器件相比,MAXll48具有单电源供电、自带内部基准电压、转换精度高、外围电路简单、占用微处理器口线少、易于连接等优点,适用于较复杂的测控系统。

ADC Maxim 电压 电路 电阻 电流 放大器 电容 电容器 电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)