MAX1148型高精度14位串行A/D转换器

时间:09-18

来源:互联网

点击:

1 概述

模/数转换器(ADC)是现代测控中非常重要的环节。它有并行和串行两种数据输出形式。并行ADC虽然数据传输速度快,但有引脚多、体积大、占用微处理器接口多的缺点;而串行ADC的传输速率目前已经可以做得很高,并且具有体积小、功耗低、占用微处理器接口少的优点。因此,串行ADC的应用越来越广泛。

MAXll48是Maxim公司最新推出的一种真差分、8通道、14位逐次逼近、串行输出模/数转换器。处理器接口多的缺点;而串行ADC的传输速率目前 该器件具有转换速率高、功耗低、接口方便的优点,特别适用于工业过程控制、高精度数据采集、便携式数字仪表、医疗仪器等领域。

2 MAX1148的特点和结构

2.1 MAX1148的特点

● 8路单端或4路差分输入(内置多路模拟开关,由软件设置)。

● 单极性模式时输出为二进制模式;

双极性模式时输出为二的补码格式,1LSB=(VREF/2N);

数据在SCLK下降沿同步输出,MSB先出。

● 5V±5%单电源。

● 内部基准电压+4.096V或外接基准。

● 采样速率:(116ksps);

120Aμ(10ksps);

12Aμ(1ksps);

300Aμ(关断模式)。

● 内置T/H(跟踪/保持)电路。

● 内部时钟或外部串行时钟(频率范围为0.1MHz"2.1MHz),可通过设置控制字中的PD1、PD0位进行选择。

● 提供一个硬关断(将SHDN引脚置低)和两个软关断(通过编程设置控制字中的PD1、PD0位来实现)模式。

● 与SPI/QSPI/MICROWIRE接口兼容。

2.2 MAX1148的结构

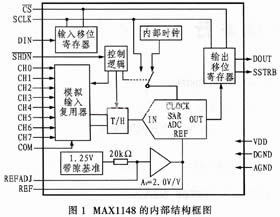

MAX1148采用14位逐次逼近寄存器(SAR)和输入跟踪/保持(T/H)电路,实现将模拟信号转换成14位数字信号,并用串行方式输出的功能,其内部结构如图1所示。

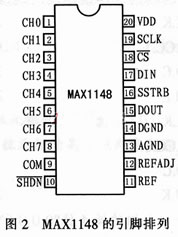

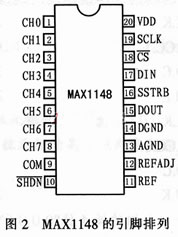

MAX1148采用20引脚的功能如下:

● CH0-CH7(1-8):模拟输入端。

● COM(9):公共输入端。单端模式下为模拟负输入。单极性和双极性模式下,当转换器输入不为0,而希望转换结果为0时,需在该端输入相应模拟电压。

● SHDN(10):关断输入,低电平有效。当SHDN置低时,转换器进入硬关断模式,转换立即中止。

● REF(11):内部基准电压输出或外部基准电压输入,它是模数转换的基准电压。该电压决定了ADC输入范围和满量程输出值。

MAX1148含有一个内部1.25V带隙基准,通过一个2kΩ电阻接至基准缓冲器并引至REFADJ引脚。由于MAX1148的基准缓冲器具有3.277V/V的增益,所以基准缓冲器输出引脚 REF直的电压为4.096V,作为内部基准电压使用。

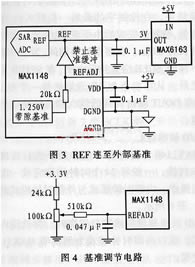

如果使用外部基准电压,则有两种使用方式:

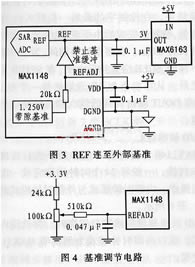

(1)禁止内部基准缓冲(将REFADJ端与VDD端直接相连),将外部基准电压(1.5V至VDD+50mV,输出电流大于210μA)接至REF端即可(如图3所示)。

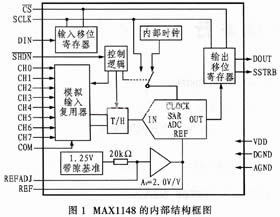

(2)将外部基准电压连至REFADJ端,通过内部基准缓冲器,在REF引脚得到幅度为外部基准电压乘以基准缓冲器增益3.277后的SAR ADC基准电压(如图4所示)需要注意的是,在REF引测得的基准电压值必须在1.5V至VDD+50mV之间。

●REFADJ(12):带隙基准输出和基准缓冲器输入。REFADJ连至VDD时禁止内部带隙基准和基准缓冲放大器,其用法如前所述。

●AGND(13):模拟地。

●DGND(14):数字地。

●DOIJT(15):串行数据输出。CS置低时,数据在SCLK下降沿同步输出。CS置高时,DOUT为高阻态。

●SsTRB(16):串行触发输出,反映了ADC转换状态。

在内部时钟模式下,ADC转换开始时,SSTRB由高变低,转换完成后,SSTRB由低变高并保持两个SCLK时钟周期为高电平。从第三个SCLK时钟周期开始,DOUT输出转换结果。

在外部时钟模式下,ADC转换开始时,SSTRB由低变高并保持两个SCLK时钟周期的高电平。从第三个SCLK时钟周期开始,在进行ADC转换的同时,DOUT输出转换结果。置高时,SSTRB为高阻。

●DIN(17):串行数据输入,用于输入控制字。CS置低时,数据在SCIK上升沿同步输入。CS置高时,DIN为高阻态。

●CS(18):片选输入,低电平有效。只有CS置低时,数据才可同步输入(DIN)或输出(DOUT)。

●SCLK(19):串行时钟输入,是数据同步输入或输出的移位信号。在外部时钟模式下,无论是SCLK还是ADC转换时钟.都决定了转换速率(SCLK的占空比必须在40%至60%之间)。

●VDD(20):电源输入。用0.1μF电容器接至AGND。

3 工作原理

3.1 控制字格式

在启动MAXll48进行A/D转换之前.必须先由SCLK将控制字从DIN端送入其内部输入移位寄存器,以决定其工作模式并启动转换。

3.2 时钟模式

MAXll48可用外部串行时钟或内部时钟两种模式来完成逐次逼近转换。但是,不管哪种模式,数据的移人和移出都要由外部时钟SCLK来完成。

在外部时钟模式下,通过外部时钟SCLK控制数据的移入和移出,同时SCLK还是模数转换时钟。在控制字的最后一位移人后,SSTRB由低变高并在保持两个SCLK时钟周期的高电平后变低。其后14个SCLK的每一个下降沿决定逐次逼近转换结果每位的值,并在DOUT端输出。需要注意的是,每次模数转换都必须在较短时间内完成,以避免采样保持电容器上的压降对转换结果带来的影响。如果外部串行时钟SCLK的频率低于100kHz。或者由于串行时钟的不连续使得转换时间超过140μs,建议使用内部时钟模式。

在内部时钟模式时,MAXll48自身产生转换时钟,并允许微处理器以小于2.1MHz的时钟频率读取转换结果。在控制字的最后一位移入后,SSTRB由高变低,待转换完成后由低变高,完成一次转换的时间最长为8.0μs。在整个转换期间,为了得到最佳的噪声性能,SCLK应保持低电平。在SSTRB变为高电平之后,从第二个SCLK开始的每一个SCLK下降沿,在DOUT端由高到低依次输出转换结果的各位的值。

模/数转换器(ADC)是现代测控中非常重要的环节。它有并行和串行两种数据输出形式。并行ADC虽然数据传输速度快,但有引脚多、体积大、占用微处理器接口多的缺点;而串行ADC的传输速率目前已经可以做得很高,并且具有体积小、功耗低、占用微处理器接口少的优点。因此,串行ADC的应用越来越广泛。

MAXll48是Maxim公司最新推出的一种真差分、8通道、14位逐次逼近、串行输出模/数转换器。处理器接口多的缺点;而串行ADC的传输速率目前 该器件具有转换速率高、功耗低、接口方便的优点,特别适用于工业过程控制、高精度数据采集、便携式数字仪表、医疗仪器等领域。

2 MAX1148的特点和结构

2.1 MAX1148的特点

● 8路单端或4路差分输入(内置多路模拟开关,由软件设置)。

● 单极性模式时输出为二进制模式;

双极性模式时输出为二的补码格式,1LSB=(VREF/2N);

数据在SCLK下降沿同步输出,MSB先出。

● 5V±5%单电源。

● 内部基准电压+4.096V或外接基准。

● 采样速率:(116ksps);

120Aμ(10ksps);

12Aμ(1ksps);

300Aμ(关断模式)。

● 内置T/H(跟踪/保持)电路。

● 内部时钟或外部串行时钟(频率范围为0.1MHz"2.1MHz),可通过设置控制字中的PD1、PD0位进行选择。

● 提供一个硬关断(将SHDN引脚置低)和两个软关断(通过编程设置控制字中的PD1、PD0位来实现)模式。

● 与SPI/QSPI/MICROWIRE接口兼容。

2.2 MAX1148的结构

MAX1148采用14位逐次逼近寄存器(SAR)和输入跟踪/保持(T/H)电路,实现将模拟信号转换成14位数字信号,并用串行方式输出的功能,其内部结构如图1所示。

MAX1148采用20引脚的功能如下:

● CH0-CH7(1-8):模拟输入端。

● COM(9):公共输入端。单端模式下为模拟负输入。单极性和双极性模式下,当转换器输入不为0,而希望转换结果为0时,需在该端输入相应模拟电压。

● SHDN(10):关断输入,低电平有效。当SHDN置低时,转换器进入硬关断模式,转换立即中止。

● REF(11):内部基准电压输出或外部基准电压输入,它是模数转换的基准电压。该电压决定了ADC输入范围和满量程输出值。

MAX1148含有一个内部1.25V带隙基准,通过一个2kΩ电阻接至基准缓冲器并引至REFADJ引脚。由于MAX1148的基准缓冲器具有3.277V/V的增益,所以基准缓冲器输出引脚 REF直的电压为4.096V,作为内部基准电压使用。

如果使用外部基准电压,则有两种使用方式:

(1)禁止内部基准缓冲(将REFADJ端与VDD端直接相连),将外部基准电压(1.5V至VDD+50mV,输出电流大于210μA)接至REF端即可(如图3所示)。

(2)将外部基准电压连至REFADJ端,通过内部基准缓冲器,在REF引脚得到幅度为外部基准电压乘以基准缓冲器增益3.277后的SAR ADC基准电压(如图4所示)需要注意的是,在REF引测得的基准电压值必须在1.5V至VDD+50mV之间。

●REFADJ(12):带隙基准输出和基准缓冲器输入。REFADJ连至VDD时禁止内部带隙基准和基准缓冲放大器,其用法如前所述。

●AGND(13):模拟地。

●DGND(14):数字地。

●DOIJT(15):串行数据输出。CS置低时,数据在SCLK下降沿同步输出。CS置高时,DOUT为高阻态。

●SsTRB(16):串行触发输出,反映了ADC转换状态。

在内部时钟模式下,ADC转换开始时,SSTRB由高变低,转换完成后,SSTRB由低变高并保持两个SCLK时钟周期为高电平。从第三个SCLK时钟周期开始,DOUT输出转换结果。

在外部时钟模式下,ADC转换开始时,SSTRB由低变高并保持两个SCLK时钟周期的高电平。从第三个SCLK时钟周期开始,在进行ADC转换的同时,DOUT输出转换结果。置高时,SSTRB为高阻。

●DIN(17):串行数据输入,用于输入控制字。CS置低时,数据在SCIK上升沿同步输入。CS置高时,DIN为高阻态。

●CS(18):片选输入,低电平有效。只有CS置低时,数据才可同步输入(DIN)或输出(DOUT)。

●SCLK(19):串行时钟输入,是数据同步输入或输出的移位信号。在外部时钟模式下,无论是SCLK还是ADC转换时钟.都决定了转换速率(SCLK的占空比必须在40%至60%之间)。

●VDD(20):电源输入。用0.1μF电容器接至AGND。

3 工作原理

3.1 控制字格式

在启动MAXll48进行A/D转换之前.必须先由SCLK将控制字从DIN端送入其内部输入移位寄存器,以决定其工作模式并启动转换。

3.2 时钟模式

MAXll48可用外部串行时钟或内部时钟两种模式来完成逐次逼近转换。但是,不管哪种模式,数据的移人和移出都要由外部时钟SCLK来完成。

在外部时钟模式下,通过外部时钟SCLK控制数据的移入和移出,同时SCLK还是模数转换时钟。在控制字的最后一位移人后,SSTRB由低变高并在保持两个SCLK时钟周期的高电平后变低。其后14个SCLK的每一个下降沿决定逐次逼近转换结果每位的值,并在DOUT端输出。需要注意的是,每次模数转换都必须在较短时间内完成,以避免采样保持电容器上的压降对转换结果带来的影响。如果外部串行时钟SCLK的频率低于100kHz。或者由于串行时钟的不连续使得转换时间超过140μs,建议使用内部时钟模式。

在内部时钟模式时,MAXll48自身产生转换时钟,并允许微处理器以小于2.1MHz的时钟频率读取转换结果。在控制字的最后一位移入后,SSTRB由高变低,待转换完成后由低变高,完成一次转换的时间最长为8.0μs。在整个转换期间,为了得到最佳的噪声性能,SCLK应保持低电平。在SSTRB变为高电平之后,从第二个SCLK开始的每一个SCLK下降沿,在DOUT端由高到低依次输出转换结果的各位的值。

ADC Maxim 电压 电路 电阻 电流 放大器 电容 电容器 电子 相关文章:

- 12位串行A/D转换器MAX187的应用(10-06)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- 12位串行A/D转换器的原理及应用开发(10-09)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 深入解析:模拟前端模/数转换器的三种类型 (11-26)