IBIS与Spice时序不匹配的问题

时间:09-20

来源:互联网

点击:

我从小就生活在旅行车里,直至长大成人。我的父母坐在前排琢磨着我们今天要去哪里。其余我们 6 个孩子则坐在后排欣赏所到之处的优美风景,虽然坐在车的后排并不是一件坏事,但我们透过车窗看到的外面的世界毕竟是有限的。

如同我的父母坐在前排一样,IBIS(I/O缓冲器信息规范)模拟模型对外界也具有强大的管理功能。他们模拟缓冲器与印刷电路板 (PCB) 交互作用的性能,但会忽略与芯片内部节点的交互作用。IBIS 模型可模拟系统级的 PCB 行为,尤其会模拟从外界到 I/O 缓冲器的连接。而另一方面,Spice 模型则可模拟芯片内部的所有晶体管。Spice 晶体管级模拟将通过输出缓冲器来分析路径,但对 PCB 感应、阻性和电容性寄生效应还有待进一步认识。

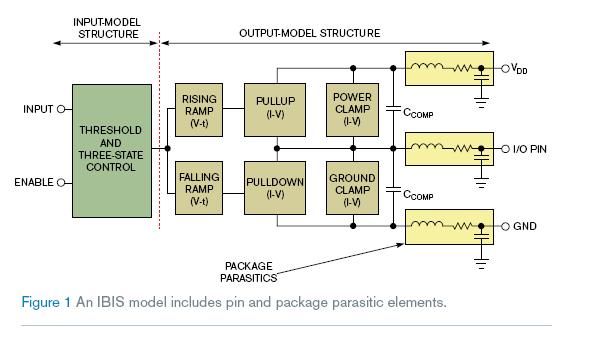

IBIS 模型为基于系统的高速模型。IBIS 模型定义了与外部(即真实的元件)交互作用的 IC 元件。在高速度时,IC 封装与 PCB 线迹寄生效应之间的交互作用对信号行为会产生很大的影响。例如,所有模型都有引脚和封装阻性、电容性和感应性的寄生元件(见图 1)。

关于精度方面,目前的 IBIS 3.2 与 4.0 模型能够精确地反映出 CMOS 缓冲器的阻抗和开关次数。尽管会有一些改进,但目前的模型仍不适合用于功率传送模拟。另外,该模型应与其源极一样精确。如果用户通过基准测试硅芯片生成了一个 IBIS 模型,则该模型将不能模拟最大和最小的统计边沿。当 IC 设计人员在收集硅芯片基准数据后仔细地重新查看其晶体管模型时,他们会发现 Spice 生成的模型是最为精确的。

模拟 IBIS 模型与其晶体管级 Spice 副本会在 IBIS 和 Spice 模拟波形之间产生不匹配问题。在波形的初始延迟之间可能存在着一定差异——输出开始转换的时间减去最初起始时间,即模拟输出曲线上的 t0。甚至在 IBIS 和 Spice 模型使用相同的激励信号和负载时,这种特定情形也会发生。这种概念或许在一开始会令人有些不安,但仔细检查会发现两组波形之间在时间上存在偏移。为什么会这样?因为 IBIS 模型就像是“坐在前排的驾驶员”,而坐在后排的“孩童”,即 Spice 模型包含通过输出缓冲器的整个延迟,并且 IBIS 模型仅表示缓冲器的外部行为。Spice 和 IBIS 模型之间在初期延迟方面的差异无关紧要,因为模型用户总是不断地将延迟“正常化”到参比条件。

IBIS 与 Spice 模型之间的相关性或许不是 100%,但速度优势总会使 IBIS 模型成为系统分析的有用工具。

如同我的父母坐在前排一样,IBIS(I/O缓冲器信息规范)模拟模型对外界也具有强大的管理功能。他们模拟缓冲器与印刷电路板 (PCB) 交互作用的性能,但会忽略与芯片内部节点的交互作用。IBIS 模型可模拟系统级的 PCB 行为,尤其会模拟从外界到 I/O 缓冲器的连接。而另一方面,Spice 模型则可模拟芯片内部的所有晶体管。Spice 晶体管级模拟将通过输出缓冲器来分析路径,但对 PCB 感应、阻性和电容性寄生效应还有待进一步认识。

IBIS 模型为基于系统的高速模型。IBIS 模型定义了与外部(即真实的元件)交互作用的 IC 元件。在高速度时,IC 封装与 PCB 线迹寄生效应之间的交互作用对信号行为会产生很大的影响。例如,所有模型都有引脚和封装阻性、电容性和感应性的寄生元件(见图 1)。

关于精度方面,目前的 IBIS 3.2 与 4.0 模型能够精确地反映出 CMOS 缓冲器的阻抗和开关次数。尽管会有一些改进,但目前的模型仍不适合用于功率传送模拟。另外,该模型应与其源极一样精确。如果用户通过基准测试硅芯片生成了一个 IBIS 模型,则该模型将不能模拟最大和最小的统计边沿。当 IC 设计人员在收集硅芯片基准数据后仔细地重新查看其晶体管模型时,他们会发现 Spice 生成的模型是最为精确的。

模拟 IBIS 模型与其晶体管级 Spice 副本会在 IBIS 和 Spice 模拟波形之间产生不匹配问题。在波形的初始延迟之间可能存在着一定差异——输出开始转换的时间减去最初起始时间,即模拟输出曲线上的 t0。甚至在 IBIS 和 Spice 模型使用相同的激励信号和负载时,这种特定情形也会发生。这种概念或许在一开始会令人有些不安,但仔细检查会发现两组波形之间在时间上存在偏移。为什么会这样?因为 IBIS 模型就像是“坐在前排的驾驶员”,而坐在后排的“孩童”,即 Spice 模型包含通过输出缓冲器的整个延迟,并且 IBIS 模型仅表示缓冲器的外部行为。Spice 和 IBIS 模型之间在初期延迟方面的差异无关紧要,因为模型用户总是不断地将延迟“正常化”到参比条件。

IBIS 与 Spice 模型之间的相关性或许不是 100%,但速度优势总会使 IBIS 模型成为系统分析的有用工具。

- 整流电路(11-30)

- 单运放构成的单稳延时电路(11-29)

- 直流稳压电源电路(11-30)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 为太阳能灯供电的低损耗电路的设计(01-22)