边界扫描SRAM簇板级互连测试研究

时间:08-30

来源:互联网

点击:

1 引言

边界扫描技术已成为了VLSI和ASIC测试的重要方法,但是,尽管边界扫描器件越来越多,非边界扫描器件仍然大量存在。在复杂电路设计中,VLSI和ASIC虽然能够完成电路的许多功能,但并不是所有的逻辑功能都可以集成,相当多的功能仍需要采用分离器件或通用集成电路实现,而它们很少支持边界扫描。因此,由边界扫描器件和非边界扫描器件组装的非完全BS器件电路板仍将在今后相当长时间内广泛存在,它们的测试问题已成为板级边界扫描测试技术需要研究的关键问题。随机存取存储器(RAM)是一种应用极为广泛的电子元件,但由于成本和结构复杂性的原因,RAM的的设计很少包含边界扫描结构,设计中也无法用其他器件所替代。

RAM可分为动态(DRAM)与静态(SRAM)两种。本文以静态SRAM为研究对象,在定义 SRAM簇的电路模型和互连故障模型的基础上,利用"虚拟数据通道"测试方法,对多驱动冲突和SRAM簇的控制线、地址线和数据线之间的板级互连故障进行分析和研究,从而提出一种更优化的测试向量生成算法,并将此算法运用于测试程序产生测试图形序列。这些测试图形序列不仅易于产生,而且有短的测试序列和高的故障覆盖率。

2 SRAM簇板级测试的基本原理

文献中提出了一种测试RAM的I/O完整性的测试序列:首先写入走步"1"的测试向量到指定地址000…000,100…000,…,000…010,000… 001,然后从各地址读回相应写入的值。文献则提出了检测RAM数据线和地址线的互连故障的测试条件,通过对这些测试条件的合并和对地址、数据线互连故障测试的组合,提出了一种新的测试算法。这种算法在文献中带有边界扫描结构的RAM簇测试的示例中已有应用。但是,上面所提到的方法都没有涉及到数据线和地址线之间的桥接故障,没有考虑BSC的多驱动冲突。下面,我们将综合上述文献的测试条件和测试矢量的优点,研究数据线和地址线之间桥接的测试条件,并确定一般性的测试条件和禁止条件,开发一个完备的SRAM簇测试矢量算法。这种算法产生的测试矢量具有以下优点:

① 能够避免多BSC驱动冲突;

② 能够覆盖所有可测SRAM互连故障;

③ 测试序列短。

下面,首先提出SRAM簇的电路模型和故障模型,然后讨论数据线、地址线、控制线以及数据线和地址线之间的固定(开路)、桥接测试条件和相应的禁止条件,这些禁止条件描述了那些不能被插入到下面所描述的测试条件中去的测试图形。最后,通过对这些测试条件和禁止条件的重新排列和组合,在综合分析的基础上得到测试矢量的具体构成,提出了一种测试算法和相应的测试图形生成程序。

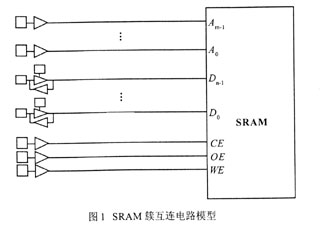

2.1 SRAM簇互连测试的电路模型

一种典型的SRAM簇的互连电路模型如图1所示。它包括:1、地址线(Am-1 ,…,A1,A0),可由2态或3态BS单元驱动;2、数据线(Dn -1,…,D1,D0 ),数据线为双向并由双向BS单元驱动;3、控制信号,包括芯片使能(CE),输出使能(OE)和写使能(WE),它们由2态或3态BS单元驱动。SRAM簇的每一个互连节点都可由多个3态的BS单元来驱动,需注意的是存在这种多驱动的情况下,必须要求任何时刻只能有一个3 态的BS单元的输出使能控制端有效,其他不能使能,以避免多驱动冲突。在本文中,我们假设只有一片SRAM,对于有多个与同一地址总线和数据总线相连的存储器芯片组成的存储器组件,只需对每一芯片分别进行互连故障测试即可,同时假定SRAM的内部逻辑无故障。

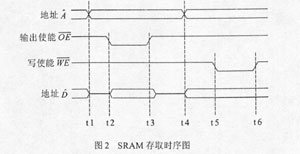

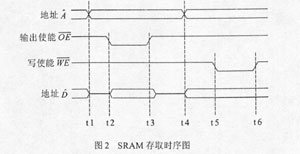

在SRAM簇的互连测试里,存储器的读写操作是通过边界扫描的"虚拟通道"来实现激励与采集,运用一组合适的测试图形序列输入到边界扫描单元中去控制地址线、数据线和控制线实现读写。图2为SRAM簇测试时实现一个SRAM的读(READ)写(WRITE)周期时序。

存储器读写信号都由写使能WE控制,WE为高电平时进行读操作,为低电平时进行写操作。同时规定地址信号、OE信号与WE信号不得同时改变。如图2所示,t1、t2和t3为一个读周期,t4、 t5和t6为一个写周期。

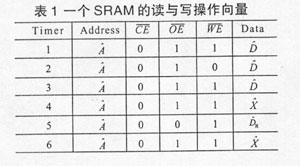

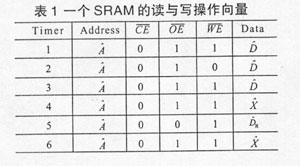

SRAM的读写操作的测试图形序列如表1所表示。表中DR表示从SRAM中读取的数据值,A和D分别表示所写数据单元的地址向量和所写数据向量,X表示任意值。本文正是按照一定的测试算法来产生SRAM簇的互连测试的测试图形。这些测试图形不仅能满足下面所描述的故障测试条件,而且能满足故障覆盖和避免多驱动冲突。

2.2 故障模式和测试条件

SRAM簇的互连故障有呆滞故障、开路故障以及在地址线、数据线和控制线间的桥接故障。SRAM簇的互连故障检测的基理是将一组测试向量的序列首先写入SRAM,读出SRAM簇的响应序列,通过分析得到互连网络上的故障行为。下面讨论是按单一故障模式分别进行,且开路故障为呆滞故障S-A-1 或S-A-0,桥接故障为"线与"或"线或"。四元组(RD,A,DR,[DE])代表对地址A的一个读操作,读取的数据值为DR,期望数据是 [DE];一个三元组(WR,A,D)代表了一个写操作,即在地址 写入数据。 和代表包含多位的向量,Ti ,j代表 的第j位。

边界扫描技术已成为了VLSI和ASIC测试的重要方法,但是,尽管边界扫描器件越来越多,非边界扫描器件仍然大量存在。在复杂电路设计中,VLSI和ASIC虽然能够完成电路的许多功能,但并不是所有的逻辑功能都可以集成,相当多的功能仍需要采用分离器件或通用集成电路实现,而它们很少支持边界扫描。因此,由边界扫描器件和非边界扫描器件组装的非完全BS器件电路板仍将在今后相当长时间内广泛存在,它们的测试问题已成为板级边界扫描测试技术需要研究的关键问题。随机存取存储器(RAM)是一种应用极为广泛的电子元件,但由于成本和结构复杂性的原因,RAM的的设计很少包含边界扫描结构,设计中也无法用其他器件所替代。

RAM可分为动态(DRAM)与静态(SRAM)两种。本文以静态SRAM为研究对象,在定义 SRAM簇的电路模型和互连故障模型的基础上,利用"虚拟数据通道"测试方法,对多驱动冲突和SRAM簇的控制线、地址线和数据线之间的板级互连故障进行分析和研究,从而提出一种更优化的测试向量生成算法,并将此算法运用于测试程序产生测试图形序列。这些测试图形序列不仅易于产生,而且有短的测试序列和高的故障覆盖率。

2 SRAM簇板级测试的基本原理

文献中提出了一种测试RAM的I/O完整性的测试序列:首先写入走步"1"的测试向量到指定地址000…000,100…000,…,000…010,000… 001,然后从各地址读回相应写入的值。文献则提出了检测RAM数据线和地址线的互连故障的测试条件,通过对这些测试条件的合并和对地址、数据线互连故障测试的组合,提出了一种新的测试算法。这种算法在文献中带有边界扫描结构的RAM簇测试的示例中已有应用。但是,上面所提到的方法都没有涉及到数据线和地址线之间的桥接故障,没有考虑BSC的多驱动冲突。下面,我们将综合上述文献的测试条件和测试矢量的优点,研究数据线和地址线之间桥接的测试条件,并确定一般性的测试条件和禁止条件,开发一个完备的SRAM簇测试矢量算法。这种算法产生的测试矢量具有以下优点:

① 能够避免多BSC驱动冲突;

② 能够覆盖所有可测SRAM互连故障;

③ 测试序列短。

下面,首先提出SRAM簇的电路模型和故障模型,然后讨论数据线、地址线、控制线以及数据线和地址线之间的固定(开路)、桥接测试条件和相应的禁止条件,这些禁止条件描述了那些不能被插入到下面所描述的测试条件中去的测试图形。最后,通过对这些测试条件和禁止条件的重新排列和组合,在综合分析的基础上得到测试矢量的具体构成,提出了一种测试算法和相应的测试图形生成程序。

2.1 SRAM簇互连测试的电路模型

一种典型的SRAM簇的互连电路模型如图1所示。它包括:1、地址线(Am-1 ,…,A1,A0),可由2态或3态BS单元驱动;2、数据线(Dn -1,…,D1,D0 ),数据线为双向并由双向BS单元驱动;3、控制信号,包括芯片使能(CE),输出使能(OE)和写使能(WE),它们由2态或3态BS单元驱动。SRAM簇的每一个互连节点都可由多个3态的BS单元来驱动,需注意的是存在这种多驱动的情况下,必须要求任何时刻只能有一个3 态的BS单元的输出使能控制端有效,其他不能使能,以避免多驱动冲突。在本文中,我们假设只有一片SRAM,对于有多个与同一地址总线和数据总线相连的存储器芯片组成的存储器组件,只需对每一芯片分别进行互连故障测试即可,同时假定SRAM的内部逻辑无故障。

在SRAM簇的互连测试里,存储器的读写操作是通过边界扫描的"虚拟通道"来实现激励与采集,运用一组合适的测试图形序列输入到边界扫描单元中去控制地址线、数据线和控制线实现读写。图2为SRAM簇测试时实现一个SRAM的读(READ)写(WRITE)周期时序。

存储器读写信号都由写使能WE控制,WE为高电平时进行读操作,为低电平时进行写操作。同时规定地址信号、OE信号与WE信号不得同时改变。如图2所示,t1、t2和t3为一个读周期,t4、 t5和t6为一个写周期。

SRAM的读写操作的测试图形序列如表1所表示。表中DR表示从SRAM中读取的数据值,A和D分别表示所写数据单元的地址向量和所写数据向量,X表示任意值。本文正是按照一定的测试算法来产生SRAM簇的互连测试的测试图形。这些测试图形不仅能满足下面所描述的故障测试条件,而且能满足故障覆盖和避免多驱动冲突。

2.2 故障模式和测试条件

SRAM簇的互连故障有呆滞故障、开路故障以及在地址线、数据线和控制线间的桥接故障。SRAM簇的互连故障检测的基理是将一组测试向量的序列首先写入SRAM,读出SRAM簇的响应序列,通过分析得到互连网络上的故障行为。下面讨论是按单一故障模式分别进行,且开路故障为呆滞故障S-A-1 或S-A-0,桥接故障为"线与"或"线或"。四元组(RD,A,DR,[DE])代表对地址A的一个读操作,读取的数据值为DR,期望数据是 [DE];一个三元组(WR,A,D)代表了一个写操作,即在地址 写入数据。 和代表包含多位的向量,Ti ,j代表 的第j位。

- 整流电路(11-30)

- 单运放构成的单稳延时电路(11-29)

- 直流稳压电源电路(11-30)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 为太阳能灯供电的低损耗电路的设计(01-22)