基于LVDS技术的远端数据传输系统实现

时间:12-07

来源:互联网

点击:

4 远端高速数据传输系统的实现

在高速远端数据传输中,信号的传输质量是整个系统功效的一个测试标准,由于高频率信号的变换较快,加上外部噪声和传输线路的衰减以及器件本身的限制等影响,高速数据系统的设计一直是工程上的一个难题。综合考虑这些因素,本系统采用串行器/解串器的方法来进行数据的传输设计。

4.1 系统工作流程

本设计是一个远端显示的系统设计,要求将接收并处理过的数据在远端显示出来。其具体过程是使发射系统每3 600μs发送一帧数据,由数据采集系统对外部信号进行A/D采样.再送入DSP中进行信号处理以得到信号的某些特征。然后由DSP将处理过的信息发送给FPGA.这些处理过的数据是6000个八位的视频数据,速率为2MB/s。FPGA先将接收到的数据存储在双口RAM中。然后从双口RAM中将数据送入串行器。并通过串行器将信号发送给传输线,远端的接收系统再通过解串器进行一个反过程以将信号恢复为八位并行数据,最后送给显示系统。其总体流程如图2所示。

4.2 数据发送及接收的实现

数据的采集及处理主要是根据具体的系统要求来获取信号的某些特征。这里着重介绍了信号的发送和接收部分以及其中用到的LVDS技术。

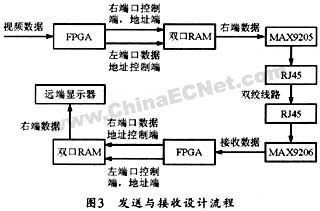

传统的高速信号送入双绞线路进行远端传输的主要是利用软件方法将并行信号转换为串行信号,然后经过差分芯片将这种单路信号转换为两路信号,再送入双绞线路进行传输,最后在接收端将接收到的信号采用软件将串行转换为并行。这种方法结构简单,软件设计也较为容易。但是,这种方法存在数据和时钟的同步问题,即在接收端很难提取到时钟信号。从而会导致传输的失败。基于此,设计时可选择串行器解串器的方法,即采用元件的内嵌时钟来自动恢复。实践证明:这种方法的确能够很好的恢复发送端的信号。发送过程和接收过程的流程图如图3所示。

目前串行器解串器产品发展十分迅速.有些产品已经突破700 Mbps的传输速率。因此,对于更高传输要求的系统设计.这种方法不失为一种很好的解决方案。

4.3 设计中应注意的问题

由于MAX9205/MAX9206工作频率较高,可以实现160~400 Mbps的数据传输率,因此。其应用要求也比较严格。下面是在系统设计和应用过程中需要注意的问题:

(1)由于串行器和解串器都存在两种电平信号(TTL乘LVDS),所以在电路板设计过程中,推荐将这两种电平信号放置在不同的层面进行走线,并在中间用电源层或地层隔开,以防两种电平信号之间出现干扰。

(2)由于信号的频率较高,所以LVDS信号走线要尽量短,并且两路差分信号走线距离要尽量相等,以防两路信号存在相位差异。减小信号的传输误差。

(3)系统的时钟信号要求比较严格,MAX9205要求时钟的抖动最大为150 ps,时钟转换时间最大为6 ns,因此,在器件的选择以及时钟线的走线上要谨慎处理。尽量保证时钟信号的质量。

(4)串行器和解串器的应用有严格要求,阻抗匹配问题也要注意,以保证接收端能够接收到正确的信号。

(5)双绞线传输媒介的平衡性也是决定信号质量的一个重要因素。

5 结束语

LVDS技术是一种低摆幅的电压差分信号,由于其抗噪声能力较强、功耗较低,目前LVDS技术能在广泛的应用领域里解决高速数据传输问题。近年来,随着体系结构技术和半导体工艺的发展,IC芯片上的时钟频率提高很快。但这也对芯片、电路底版、机箱以及机柜之间的互连速度提出了更迫切的要求。现代高性能微处理器的速度已经突破了1 GHz,芯片间的传输速率也达到了几百兆赫兹。但是,常规的CMOS和TTL由于自身的电路特性和信号特点。很难在芯片外进行200 MHz以上的信号传输。因此,大多数的微处理器的外部工作频率都降低到内部的一半,甚至更低。这就大大限制了微处理器高速性能的发挥。对于这个问题,LVDS技术也可作为一个有效的解决方法。因此,LVDS技术必将具有广泛的应用前景。基于LVDS技术电路的模块也必将得到更广泛的应用。

在高速远端数据传输中,信号的传输质量是整个系统功效的一个测试标准,由于高频率信号的变换较快,加上外部噪声和传输线路的衰减以及器件本身的限制等影响,高速数据系统的设计一直是工程上的一个难题。综合考虑这些因素,本系统采用串行器/解串器的方法来进行数据的传输设计。

4.1 系统工作流程

本设计是一个远端显示的系统设计,要求将接收并处理过的数据在远端显示出来。其具体过程是使发射系统每3 600μs发送一帧数据,由数据采集系统对外部信号进行A/D采样.再送入DSP中进行信号处理以得到信号的某些特征。然后由DSP将处理过的信息发送给FPGA.这些处理过的数据是6000个八位的视频数据,速率为2MB/s。FPGA先将接收到的数据存储在双口RAM中。然后从双口RAM中将数据送入串行器。并通过串行器将信号发送给传输线,远端的接收系统再通过解串器进行一个反过程以将信号恢复为八位并行数据,最后送给显示系统。其总体流程如图2所示。

4.2 数据发送及接收的实现

数据的采集及处理主要是根据具体的系统要求来获取信号的某些特征。这里着重介绍了信号的发送和接收部分以及其中用到的LVDS技术。

传统的高速信号送入双绞线路进行远端传输的主要是利用软件方法将并行信号转换为串行信号,然后经过差分芯片将这种单路信号转换为两路信号,再送入双绞线路进行传输,最后在接收端将接收到的信号采用软件将串行转换为并行。这种方法结构简单,软件设计也较为容易。但是,这种方法存在数据和时钟的同步问题,即在接收端很难提取到时钟信号。从而会导致传输的失败。基于此,设计时可选择串行器解串器的方法,即采用元件的内嵌时钟来自动恢复。实践证明:这种方法的确能够很好的恢复发送端的信号。发送过程和接收过程的流程图如图3所示。

目前串行器解串器产品发展十分迅速.有些产品已经突破700 Mbps的传输速率。因此,对于更高传输要求的系统设计.这种方法不失为一种很好的解决方案。

4.3 设计中应注意的问题

由于MAX9205/MAX9206工作频率较高,可以实现160~400 Mbps的数据传输率,因此。其应用要求也比较严格。下面是在系统设计和应用过程中需要注意的问题:

(1)由于串行器和解串器都存在两种电平信号(TTL乘LVDS),所以在电路板设计过程中,推荐将这两种电平信号放置在不同的层面进行走线,并在中间用电源层或地层隔开,以防两种电平信号之间出现干扰。

(2)由于信号的频率较高,所以LVDS信号走线要尽量短,并且两路差分信号走线距离要尽量相等,以防两路信号存在相位差异。减小信号的传输误差。

(3)系统的时钟信号要求比较严格,MAX9205要求时钟的抖动最大为150 ps,时钟转换时间最大为6 ns,因此,在器件的选择以及时钟线的走线上要谨慎处理。尽量保证时钟信号的质量。

(4)串行器和解串器的应用有严格要求,阻抗匹配问题也要注意,以保证接收端能够接收到正确的信号。

(5)双绞线传输媒介的平衡性也是决定信号质量的一个重要因素。

5 结束语

LVDS技术是一种低摆幅的电压差分信号,由于其抗噪声能力较强、功耗较低,目前LVDS技术能在广泛的应用领域里解决高速数据传输问题。近年来,随着体系结构技术和半导体工艺的发展,IC芯片上的时钟频率提高很快。但这也对芯片、电路底版、机箱以及机柜之间的互连速度提出了更迫切的要求。现代高性能微处理器的速度已经突破了1 GHz,芯片间的传输速率也达到了几百兆赫兹。但是,常规的CMOS和TTL由于自身的电路特性和信号特点。很难在芯片外进行200 MHz以上的信号传输。因此,大多数的微处理器的外部工作频率都降低到内部的一半,甚至更低。这就大大限制了微处理器高速性能的发挥。对于这个问题,LVDS技术也可作为一个有效的解决方法。因此,LVDS技术必将具有广泛的应用前景。基于LVDS技术电路的模块也必将得到更广泛的应用。

电压 总线 PCB 电流 CMOS 电阻 电路 模拟电路 DSP FPGA 半导体 相关文章:

- 不用软件工具能开展设计吗?(02-28)

- 保护CAN总线收发器不受静电释放和瞬态电压影响的方法(03-22)

- 基于C5509A的功放闭环数字控制系统(01-28)

- HSP3824扩频通信芯片的功能及应用(04-08)

- 通信系统中超高效率Buck变换器设计考虑(05-02)

- 智能化网络家电控制中电力载波模块的设计(03-23)