基于LVDS技术的远端数据传输系统实现

时间:12-07

来源:互联网

点击:

1 引言

现在,各种系列的传输设备或传输系统均使用价格便宜、取材方便的双绞线。来传输高质量的视频信号、音频信号和控制数据。且其传输距离可选。虽然使用品牌系列双绞线所组成的传输系统具有独特亮度/色度处理、多级瞬态冲击保护及超强的干扰抑制能力,但在数据高速传输中,其高可靠性技术指标却并不能符合要求,其所面临的问题是如何应用先进的技术来保证数据在双绞线缆中的高速传输。而将低电压差分信号(LVDS)串行器一解串器用于双绞线电缆数据高速传输系统不失为一种新技术,MAXIM公司的MAX9205/MAX9206正是利用这种技术完成了高频信号的远端传输。

2 LVDS技术及其优势

LVDS接口又称RS-644总线接口,是20世纪90年代出现的一种数据传输和接口技术。LVDS是一种小振幅差分信号技术,使用非常低的幅度信号(约350 mV),它通过一对差分PCB走线或平衡电缆来传输数据。其单个信道传输速率可达到每秒数百兆比特。其特有的低振幅及恒流源驱动方式只产生极低的噪声,且其功耗非常小。其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS技术和其它接口相比。有着很大的优势,主要表现在下面几个方面:

(1)高速率

由于LVDS逻辑状态间的电压变化仅为300mV,因而能非常快地改变状态,从而实现高速率。

(2)低功耗

随着工作频率的增加,LVDS的电源电流仍保持平坦,而CMOS和TTL技术的电源电流则会随频率增加而指数上升,这得益于使用恒流线路驱动器。LVDS的电流源可把输出电流限制到约3.5mA,同时也能限制跳变期间产生的任何尖峰电流。这样,在得到高达1.5 Gbps的高数据率的同时却不明显增加功耗。恒流驱动输出还能容忍传输线的短路或接地而不会产生热问题。由于LVDS降低了终端电阻压降,因此也降低了电路的总功耗。

(3)噪声性能好

LVDS产生的电磁干扰很低,这是因为采用了低电压摆幅、低边沿速率、奇模式差分信号、恒流驱动器的原因。其Icc尖峰只产生很低的辐射。通过减小电压摆幅和电流能量,LVDS可把场强减到了最小;其差分驱动器还引入了奇模式传输,即等量方向相反的电流分别在传输线上传输。以形成电流环路。从而使电流回路产生最低的电磁干扰;在差分信号的传输中,由于差分接收器只响应正负输入之差,因此当噪声同时出现在两个输入中时,其差分信号的幅度并不受影响。

(4)具有故障安全(fail-safe)特性

由于恒流式驱动不会对系统造成任何损害,所以,LVDS驱动器可以带电插拔。LVDS的另一特点是接收器的故障保护功能,LVDS接收器在内部提供了可靠性线路。故可保证在接收器输入悬空、短路以及接收器输入处于驱动器三态输出或驱动器供电终止等情况下的可靠输出(约定为“1”),从而防止输出产生振荡。

(5)集成能力强

由于可在标准的CMOS工艺中实现高速LVDS,故采用LVDS模拟电路集成复杂的数字功能是非常有利的。

基于LVDS技术的众多优点。面向LVDS的电路模块越来越多。本文的LVDS串行器/解串器MAX9205/MAX9206就是其中最典型的一对器件。

3 MAX9205和MAX9206概述

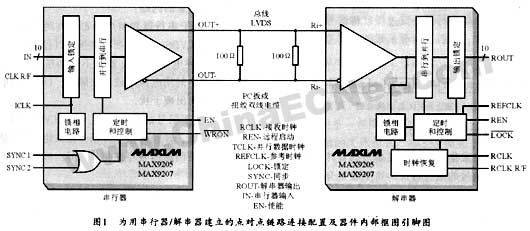

MAX9205和MAX9206是美信公司推出的一组差分信号芯片组。其中MAX9205可将1O位并行COM数据或TTL数据转换成具有内嵌时钟的高速串行数据流;MAX9206则是可接收该串行数据流并将它们转换为并行数据的解串器。同时又可以重建并行时钟。该器件组进行数据转换采用的是内嵌时钟,这样就可有效的解决由于时钟与数据的不严格同步而制约高速传输的瓶颈问题。MAX9205/MAX9206的内部结构及应用方法如图1所示。

3.1 MAX9205和MAX9206的工作原理

MAX9205 LVDS串行器和MAX9206 LVDS解串器能够通过差分特性阻抗为100 Ω的串行点对点链路来传输高速数据。MAX9205和MAX9206的并行时钟频率范围为16~40 MHz。在数据转换的时候,串行器元件内部将自动加上两个数据位,即在并行送入的10位数据中加上一个起始位(1)和一个终止位(0),这样,串行器输出就形成了一个12位的串行数据流,而解串器在接收数据的同时,则根据接收数据终止位和起始位之间的上升沿来恢复并行时钟频率。

3.2 MAX9205/MAX9206的工作模式

MAX9205和MAX9206具有初始化、同步模式、数据传输模式和节电模式这四种工作状态.现分别介绍如下:

(1)初始化

上电后,各个管脚的输出为高阻状态.之后启动锁相环工作并跟随本地时钟,一旦锁存时钟信号后,就可以准备发送数据信号。

(2)同步模式

MAX9205具有两个同步模式选择位SYNC1和SYNC2,初始化之后就可以根据这两位的状态来决定芯片是进行同步模式还是数据传输模式。当两者之中有一个管脚持续6个周期的高状态后.芯片就会传输1024个周期的同步信号。同步信号是由6个连续的0和6个连续的1组成的串行数据流。

(3)数据传输模式

初始化完成后,若同步管脚都为0。则进行数据传输。此时串行器用TCLK端选通输入数据并存入10位输入锁存器。发送时从中取出数据,再加上作为内嵌时钟的起始位(1)和终止位(0)各一位,将总共12位数据顺序发送至串行差分端口,然后由解串器将接收到的串行数据转换为10位并行数据并存入输出锁存器,同时从内嵌时钟中恢复并重建并行时钟,并以此时钟来选通输出锁存器及输出数据。

(4)节电模式

串行器和解串器均可以工作在节电模式。当没有数据传输时,可以通过设置管脚pwden将芯片置于节电模式。这时锁相环停止工作,输出为三态,电流也降低到几个毫安。

现在,各种系列的传输设备或传输系统均使用价格便宜、取材方便的双绞线。来传输高质量的视频信号、音频信号和控制数据。且其传输距离可选。虽然使用品牌系列双绞线所组成的传输系统具有独特亮度/色度处理、多级瞬态冲击保护及超强的干扰抑制能力,但在数据高速传输中,其高可靠性技术指标却并不能符合要求,其所面临的问题是如何应用先进的技术来保证数据在双绞线缆中的高速传输。而将低电压差分信号(LVDS)串行器一解串器用于双绞线电缆数据高速传输系统不失为一种新技术,MAXIM公司的MAX9205/MAX9206正是利用这种技术完成了高频信号的远端传输。

2 LVDS技术及其优势

LVDS接口又称RS-644总线接口,是20世纪90年代出现的一种数据传输和接口技术。LVDS是一种小振幅差分信号技术,使用非常低的幅度信号(约350 mV),它通过一对差分PCB走线或平衡电缆来传输数据。其单个信道传输速率可达到每秒数百兆比特。其特有的低振幅及恒流源驱动方式只产生极低的噪声,且其功耗非常小。其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS技术和其它接口相比。有着很大的优势,主要表现在下面几个方面:

(1)高速率

由于LVDS逻辑状态间的电压变化仅为300mV,因而能非常快地改变状态,从而实现高速率。

(2)低功耗

随着工作频率的增加,LVDS的电源电流仍保持平坦,而CMOS和TTL技术的电源电流则会随频率增加而指数上升,这得益于使用恒流线路驱动器。LVDS的电流源可把输出电流限制到约3.5mA,同时也能限制跳变期间产生的任何尖峰电流。这样,在得到高达1.5 Gbps的高数据率的同时却不明显增加功耗。恒流驱动输出还能容忍传输线的短路或接地而不会产生热问题。由于LVDS降低了终端电阻压降,因此也降低了电路的总功耗。

(3)噪声性能好

LVDS产生的电磁干扰很低,这是因为采用了低电压摆幅、低边沿速率、奇模式差分信号、恒流驱动器的原因。其Icc尖峰只产生很低的辐射。通过减小电压摆幅和电流能量,LVDS可把场强减到了最小;其差分驱动器还引入了奇模式传输,即等量方向相反的电流分别在传输线上传输。以形成电流环路。从而使电流回路产生最低的电磁干扰;在差分信号的传输中,由于差分接收器只响应正负输入之差,因此当噪声同时出现在两个输入中时,其差分信号的幅度并不受影响。

(4)具有故障安全(fail-safe)特性

由于恒流式驱动不会对系统造成任何损害,所以,LVDS驱动器可以带电插拔。LVDS的另一特点是接收器的故障保护功能,LVDS接收器在内部提供了可靠性线路。故可保证在接收器输入悬空、短路以及接收器输入处于驱动器三态输出或驱动器供电终止等情况下的可靠输出(约定为“1”),从而防止输出产生振荡。

(5)集成能力强

由于可在标准的CMOS工艺中实现高速LVDS,故采用LVDS模拟电路集成复杂的数字功能是非常有利的。

基于LVDS技术的众多优点。面向LVDS的电路模块越来越多。本文的LVDS串行器/解串器MAX9205/MAX9206就是其中最典型的一对器件。

3 MAX9205和MAX9206概述

MAX9205和MAX9206是美信公司推出的一组差分信号芯片组。其中MAX9205可将1O位并行COM数据或TTL数据转换成具有内嵌时钟的高速串行数据流;MAX9206则是可接收该串行数据流并将它们转换为并行数据的解串器。同时又可以重建并行时钟。该器件组进行数据转换采用的是内嵌时钟,这样就可有效的解决由于时钟与数据的不严格同步而制约高速传输的瓶颈问题。MAX9205/MAX9206的内部结构及应用方法如图1所示。

3.1 MAX9205和MAX9206的工作原理

MAX9205 LVDS串行器和MAX9206 LVDS解串器能够通过差分特性阻抗为100 Ω的串行点对点链路来传输高速数据。MAX9205和MAX9206的并行时钟频率范围为16~40 MHz。在数据转换的时候,串行器元件内部将自动加上两个数据位,即在并行送入的10位数据中加上一个起始位(1)和一个终止位(0),这样,串行器输出就形成了一个12位的串行数据流,而解串器在接收数据的同时,则根据接收数据终止位和起始位之间的上升沿来恢复并行时钟频率。

3.2 MAX9205/MAX9206的工作模式

MAX9205和MAX9206具有初始化、同步模式、数据传输模式和节电模式这四种工作状态.现分别介绍如下:

(1)初始化

上电后,各个管脚的输出为高阻状态.之后启动锁相环工作并跟随本地时钟,一旦锁存时钟信号后,就可以准备发送数据信号。

(2)同步模式

MAX9205具有两个同步模式选择位SYNC1和SYNC2,初始化之后就可以根据这两位的状态来决定芯片是进行同步模式还是数据传输模式。当两者之中有一个管脚持续6个周期的高状态后.芯片就会传输1024个周期的同步信号。同步信号是由6个连续的0和6个连续的1组成的串行数据流。

(3)数据传输模式

初始化完成后,若同步管脚都为0。则进行数据传输。此时串行器用TCLK端选通输入数据并存入10位输入锁存器。发送时从中取出数据,再加上作为内嵌时钟的起始位(1)和终止位(0)各一位,将总共12位数据顺序发送至串行差分端口,然后由解串器将接收到的串行数据转换为10位并行数据并存入输出锁存器,同时从内嵌时钟中恢复并重建并行时钟,并以此时钟来选通输出锁存器及输出数据。

(4)节电模式

串行器和解串器均可以工作在节电模式。当没有数据传输时,可以通过设置管脚pwden将芯片置于节电模式。这时锁相环停止工作,输出为三态,电流也降低到几个毫安。

电压 总线 PCB 电流 CMOS 电阻 电路 模拟电路 DSP FPGA 半导体 相关文章:

- 不用软件工具能开展设计吗?(02-28)

- 保护CAN总线收发器不受静电释放和瞬态电压影响的方法(03-22)

- 基于C5509A的功放闭环数字控制系统(01-28)

- HSP3824扩频通信芯片的功能及应用(04-08)

- 通信系统中超高效率Buck变换器设计考虑(05-02)

- 智能化网络家电控制中电力载波模块的设计(03-23)