SoC设计中的片上通信体系结构研究

时间:10-12

来源:互联网

点击:

2 一种新的片上通信体系结构

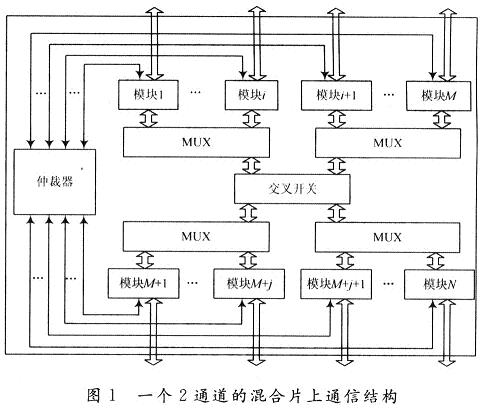

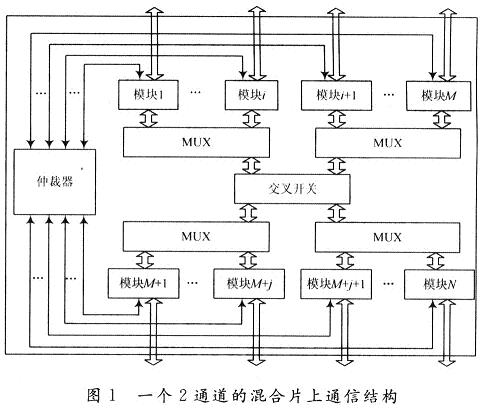

据市场预测,2010年全球市场SoC规模将超过IC总市场份额,因此作为SoC设计的关键技术之一的片上通信的研究与设计,具有重要意义。在国内外研究片上通信体系结构的基础上,提出一种将共享总线和片上网络相结合的混合片上通信结构。图1给出了一个2通道混合片上通信结构的示意图。该混合片上通信体系结构,传统的片上共享总线与片上网络相结合。这样,对于具有N个主从设备的IP核的SoC,经配置M个通道可以并行通信。

图1中的仲裁器用于对所有模块的通信申请和授权进行仲裁。这里提出了基于申请和授权的优先级模型。

仲裁序列:在SoC中存在N个主设备,记为M1,M2,…,Mi,…,MN(i=1,2,…,N),如果将第i次得到仲裁的主设备记为Xi,那么称序列{X1,X2,…,Xi,…}为仲裁序列。

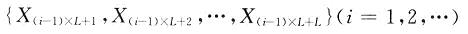

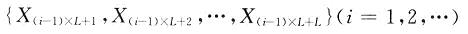

仲裁周期序列段:如果仲裁周期为L(正整数),那么第i个仲裁周期序列段为:

Mi到Mj的授权转移:如果Xi为Mi,Xi+1为Mi,那么称{Xi,Xi+1}为Mi到Mj的授权转移。

授权模式:在第i个仲裁周期序列段{X(i-1)×L+1,X(i-1)×L+2,…,X(i-1)×L+L}(i=1,2,…)中,如果第j个主设备的授权次数记为nj(j=1,2,…,N),那么{n1,n2,…,nj,…,nN}称为第i个仲裁周期序列的授权模式。

由授权模式和仲裁周期的定义,可以得到:

通常,在某一运行时间段,SoC中的各个IP核的优先级将不同于另一个运行的时间段,因此,SoC中各个IP核优先级必然存在时间局域性。在此前提下,利用存储的第i个仲裁周期序列段中的授权模式,可以动态计算第i+1个仲裁周期序列段中的Xi×L+j=Mk(k=1,2,…,N)的机率和Mi~Mj的授权转移机率。

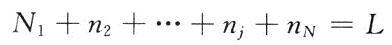

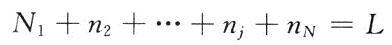

图1中,进行数据报文交换的是交叉开关。如果在SoC中仅有一个或两个DSP,该交叉开关可以有2M个端口;而如果存在一个处理器(DSP)阵列,则该交叉开关可以有2M+1个端口,以便于二维网格的扩展。图1中的MUX单元可以采用选通器,如图2所示。

目前已经完成对仲裁器、接口单元和片上交叉开关进行Verilog的RTL代码编写,在Cadence的仿真环境下进行了功能验证。下一步将针对TSMC的180 nm低功耗标准单元库进行逻辑综合,在Cadence的仿真环境下得到面积、功耗和主频等性能参数,并完成对上述片上通信结构后端的设计和评估。

3 结 语

经验证,该片上通信的优化体系结构既保留了片上共享总线的面积小的优点,又具有片上网络的并行通信的优点。目前,具有优化体系结构的片上通信IP核,已经应用于实际的SoC设计中。将来,该研究结果在我国已发展或将要发展的高清晰度数字电视处理器SoC芯片、3G无线移动终端基带SoC芯片和其他SoC芯片的设计中,都会具有重要的实际应用意义。

据市场预测,2010年全球市场SoC规模将超过IC总市场份额,因此作为SoC设计的关键技术之一的片上通信的研究与设计,具有重要意义。在国内外研究片上通信体系结构的基础上,提出一种将共享总线和片上网络相结合的混合片上通信结构。图1给出了一个2通道混合片上通信结构的示意图。该混合片上通信体系结构,传统的片上共享总线与片上网络相结合。这样,对于具有N个主从设备的IP核的SoC,经配置M个通道可以并行通信。

图1中的仲裁器用于对所有模块的通信申请和授权进行仲裁。这里提出了基于申请和授权的优先级模型。

仲裁序列:在SoC中存在N个主设备,记为M1,M2,…,Mi,…,MN(i=1,2,…,N),如果将第i次得到仲裁的主设备记为Xi,那么称序列{X1,X2,…,Xi,…}为仲裁序列。

仲裁周期序列段:如果仲裁周期为L(正整数),那么第i个仲裁周期序列段为:

Mi到Mj的授权转移:如果Xi为Mi,Xi+1为Mi,那么称{Xi,Xi+1}为Mi到Mj的授权转移。

授权模式:在第i个仲裁周期序列段{X(i-1)×L+1,X(i-1)×L+2,…,X(i-1)×L+L}(i=1,2,…)中,如果第j个主设备的授权次数记为nj(j=1,2,…,N),那么{n1,n2,…,nj,…,nN}称为第i个仲裁周期序列的授权模式。

由授权模式和仲裁周期的定义,可以得到:

通常,在某一运行时间段,SoC中的各个IP核的优先级将不同于另一个运行的时间段,因此,SoC中各个IP核优先级必然存在时间局域性。在此前提下,利用存储的第i个仲裁周期序列段中的授权模式,可以动态计算第i+1个仲裁周期序列段中的Xi×L+j=Mk(k=1,2,…,N)的机率和Mi~Mj的授权转移机率。

图1中,进行数据报文交换的是交叉开关。如果在SoC中仅有一个或两个DSP,该交叉开关可以有2M个端口;而如果存在一个处理器(DSP)阵列,则该交叉开关可以有2M+1个端口,以便于二维网格的扩展。图1中的MUX单元可以采用选通器,如图2所示。

目前已经完成对仲裁器、接口单元和片上交叉开关进行Verilog的RTL代码编写,在Cadence的仿真环境下进行了功能验证。下一步将针对TSMC的180 nm低功耗标准单元库进行逻辑综合,在Cadence的仿真环境下得到面积、功耗和主频等性能参数,并完成对上述片上通信结构后端的设计和评估。

3 结 语

经验证,该片上通信的优化体系结构既保留了片上共享总线的面积小的优点,又具有片上网络的并行通信的优点。目前,具有优化体系结构的片上通信IP核,已经应用于实际的SoC设计中。将来,该研究结果在我国已发展或将要发展的高清晰度数字电视处理器SoC芯片、3G无线移动终端基带SoC芯片和其他SoC芯片的设计中,都会具有重要的实际应用意义。

集成电路 半导体 SoC 电路 电子 总线 ARM 自动化 编码器 电压 DSP Verilog Cadence 仿真 数字电视 相关文章:

- 高性能、高集成度的TD-SCDMA模拟基带集成电路的实现和应用(01-09)

- Vitesse芯片组提升高密度40G/100G光学系统性能(02-25)

- 无线设备中CMOS频率源的应用趋势(05-08)

- 光互连技术(12-29)

- 利用串行RapidIO交换机设计模块化无线基础系统(03-12)

- 基于FPGA的USB接口IP核设计(03-13)