高性能、高集成度的TD-SCDMA模拟基带集成电路的实现和应用

作为中国原创技术,与WCDMA及CDMA2000并列的第三代移动通信标准--TD-SCDMA技术已步入实用化阶段。随着TD-SCDMA产业联盟的成立和发展,以产业联盟为核心的覆盖集成电路、设备、系统、终端和科研的产业链已基本形成。随着TD-SCDMA试验网在北京、成都、重庆三地开通和现场测试的开展,对TD-SCDMA的发展已无多少悬念。然而TD-SCDMA的各种技术优势并不能够解决其技术形成晚的问题,国内的TD-SCDMA的产业化和商业化均无法与WCDMA和CDMA2000相比,特别是在集成电路研发方面。

TD-SCDMA手机终端的核心由射频(RFIC)、模拟基带(ABB)和数字基带(DBB)组成。现今手机通常采用双芯片解决方案,即射频芯片和基带芯片。前者涵盖了射频接收、发射、频率合成和功率放大等功能,后者则包含了模拟基带和数字基带功能,分别实现信号处理和协议处理。现在独立的ABB芯片已不多见,如Maxim公司的MAX19700。但在产业化初期阶段,研发TD-SCDMA专用的ABB芯片仍然有意义。

首先DBB芯片是一款纯数字芯片,因此DBB芯片可以随着CMOS制造工艺的演进而演进,而ABB芯片作为一款典型的混合信号芯片,其成本对工艺并不敏感。其次集成基带解决方案主要是为了降低终端设计难度和制造成本,但如果能够合理分配功能,提高各自的集成度,分离的解决方案同样具备竞争力。同时分离方案有利于降低各自的研发成本、缩短研发周期、加快实用化进程,在现阶段对于TD-SCDMA这样的新兴技术是可行和有利的。为此捷顶微电子(上海)有限公司推出了一款TD-SCDMA终端专用的ABB芯片--AS2003。

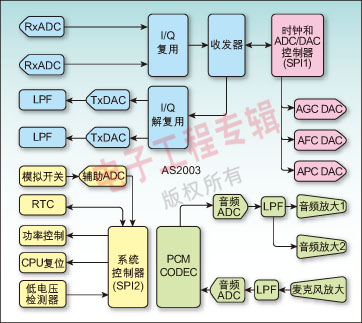

AS2003是一颗高性能、高集成度的TD-SCDMA终端专用ABB信号处理芯片,其内部架构见图1。芯片中集成有多路中频信号数模和模数转换电路、中频信号放大器、低通滤波器、多路辅助数模转换电路和单路带选通开关的多路输入辅助模数转换电路。此外AS2003还集成了完整的音频处理电路和辅助电源管理电路,包括带双路输入和双路输出的单声道音频编解码器,音频功率放大器,可用于电池电压或温度信号检测的辅助模数转换电路、开关机检测电路和低电压监测保护电路,集成的实时时钟可提供丰富的定时功能。采用1.8/3.0V供电的AS2003有着优秀的信号处理性能和极低的功耗,收发通道电路工作的典型电流仅10mA,在关机和实时时钟工作时,工作电流仅有5uA,可明显延长终端的通话时间和待机时间。Mini-BGA的封装和极少的外围被动元件需求可有效节省PCB面积、简化终端设计、降低成本。

AS2003的实现

ABB芯片最基本的功能就是实现对正交中频信号的模数/数模转换,因此需要双路ADC处理RF芯片输出的正交模拟I/Q中频信号、双路DAC处理DBB芯片生成的正交数字I/Q中频信号。这些ADC和DAC要有合适的采样和转换精度及速率、高信噪比、高无杂散动态范围、优良的相位和增益匹配度。

图1:AS2003内部架构示意图

AS2003采用双路10位ADC和双路10位DAC,支持最高5.12Msps采样频率的设计。当输入640kHz模拟中频信号,采样率为5.12Msps时,ADC的SINAD达到54.9dB,SFDR可达78dBc。配合集成的全差分输入放大器,I/Q通道的相位匹配度可达±0.22°,增益匹配度为±0.02dB。

在中频发送电路部分集成了一可选通的带宽640kHz的低通滤波器,其旁瓣抑制大于55dB。当低通滤波器工作时,DAC的阻带抑制大于55dB,典型的I/Q通道的相位匹配度可达±0.16°,增益匹配度为±0.05dB,并可通过调节输出共模电压来调节I/Q信号的失调。

ADC和DAC共享的高速数据总线,在满足TD-SCDMA时分双工(TDD)工作模式的前提下进行了优化设计。数据总线由ADC I/Q复用电路、DAC I/Q解复用电路和收发双工电路共同实现,接口采用半双工模式,DBB芯片可通过改变发射/接收(Tx/Rx)信号来控制数据传输方向。为了降低对时钟频率的要求,AS2003采用双速率模式设计,即在时钟的上下沿均传输数据,上边沿传输I路数据,下边沿传输Q路数据。

除了射频信号外,DBB芯片需要通过改变射频前端电路的各类放大电路的增益来调整接收灵敏度和发射功率,同时还要通过调整射频前端电路的频率合成器来改变射频频率。为此AS2003集成了三路独立的12位精度辅助DAC,可分别用于生成RF芯片中的接收放大器,频率合成器和发送放大器的模拟控制信号。这些DAC通过SPI接口接受来自DBB芯片的控制数据,在连接20kΩ负载时每路DAC的建立时间小于0.3us,这种快速建立特性能有效地保证DBB芯片对RF芯片的实时调整。

在手机终端中音频处理是一重要组成部分,其性能直接影响用户的

- WiMax可能和TD-SCDMA一起上 英特尔图谋中国3G(08-23)

- TD-SCDMA测试用户过两万 中国标准着眼4G(08-23)

- 全球WiMAX论坛主席Ronald Resnick演讲(08-23)

- 3G市场规模预测:运营格局决定市场规模(08-30)

- 3G及TD-SCDMA务实发展策略思考(08-30)

- 大唐电信总裁曹斌:TD-SCDMA基本可以商用(08-30)