1.1GHz集成单片锁相频率合成器MC145190

时间:09-18

来源:互联网

点击:

2 MC145190/191/192的数据格式与编程

MC145190/191/192的C、R、A寄存器均为箝位寄存器,数据流的输入不需要地址和控制信号,而是由数据流的字长度来决定输入到哪个寄存器。8个时钟周期的数据流移入C寄存器,16个时钟周期的数据流移入R寄存器,24个时钟周期的数据流移入A寄存器。数据流按高位顺序先移入,而C、R、A的有效位则按低位顺序计算。

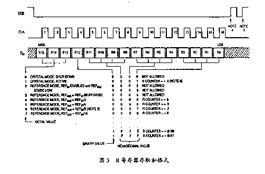

R寄存器的存取和数据格式如图3所示。高位R15、R14、R13的控制功能如图中所示,低位R0 ~ R12为13位R计数器的数据内容,R=0~8191。

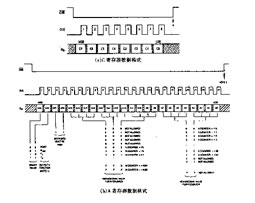

C寄存器为8位控制寄存器,数据格式如图4(a)中所示。

C7-POL位用以选择鉴相器的输出极性。当C7=1时,PDout输出反极性,且ΦR和Φv互换功能;C7=0时,PDout输出正极性,且ΦR和Φv功能不变。

C6-PDA/B位用以选择鉴相器PDA或PDB:C6=1时选用PDA,而PDB则禁止;C6=0时则选用PDB,PDA这时被禁用。

C5-LDE位为环路锁定指示检测位,该位通常置“0”。C4-STBY位用以控制器件处于睡眠备用状态,可节省功耗。

C4=1时,PDout和ΦR、Φv均处高阻状态,且Rx电流关断,A、N、R计数器停止计数,这时器件处于睡眠备用状态;C4=0时,PDout和ΦR、Φv,以及A、N、R计数器进入正常工作状态。

C3、C2位用以控制PDout流入流出电流的大小,当这两位均置高位“1”时,可得到最大电流100%。PDout电流的大小步长还受C1-port数据控制。当OutputA不作数据端口使用时〔通过A寄存器中的A23、A22位置数控制,见图4(b)A寄存器存取和数据格式图〕。

C1=0, 则PDout按10%步长变化电流,C1=1, 则PDout按25%步长变化电流。OutputA用作数据端口使用时,则C1决定OutputA的状态,C1=1, 则Output A为高,C1=0, 则Output A为低。

C0-outB位决定Output B的状态,C0=1时Output B为高,C0=0时Output B为低。

A寄存器的数据格式如图4(b)中所示,A寄存器为24位箝位寄存器。其中高4位为控制码,A23、A22确定OutputA的输出功能,A21

、A20为内部逻辑控制码,必须都置“1”。A0~A7为8位脉冲吞除计数器的数据码A=0~255,A8~A11为12位主计数器N的数据码N=5~4095,N禁止小于5。显然N计数器的容量大于A计数容量。在环路设计时,也必须是N>A。

3 应用设计举例

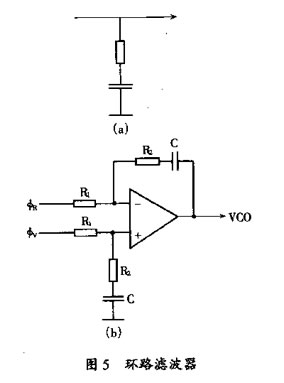

采用MC145109/191/192设计单环频率合成器时,必须外接环路滤波器和配上一只相应的压控振荡器VCO。外接环路滤波器的结构如图5所示,图5(a)适用于PDA,即接于PDAout输出端,这时环路设计关系式为KΦ·KVCO=ωn2 * MC和2ζ=ωnRC,式中M为环路分频比。

图5(b)适用于PDB,这是一个有源滤波器,环路设计关系式为KΦKVCO=ωn2MCR1和2ζ=ωnR2C。

采用PDA的PDout输出图5(a)时,鉴相增益KΦ=Ipout/2πA/rad。Ipout为PDout的流入流出电流,前面已指出由C寄存器控制码和Rx确定其值。

若采用PDB的图5(b)有源滤波器时,KΦ=VPD/2πV/rad。

下面以移动通信GSM频段频率合成器为例,介绍MC145191的应用设计方法。移动通信GSM标准的合作频段为935~960MHz和890~915MHz,双工间隔为45MHz,频道间隔为200kHz,换频时间小于5ms。以935~960MHz频段为例,该频率合成器的VCO应满足的频率范围为:

2f0min-f0max=2*935-960=910MHz,

2f0max-f0min=2*960-935=985MHz

变容管的控制电压调谐范围为1~5.5V,则压控灵敏度为:

K0 =(985-910)/(5.5-1) = 17*106(Hz/V)=2π*17*106(rad/s/V)

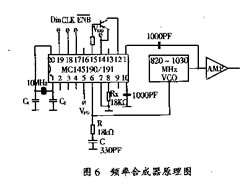

频率合成器的原理图如图6中所示。

单环频率合成器的频率间隔△f0=fR=200kHz,图中采用10MHz晶振。R寄存器的R15、R14、R13置成001,REFin?和REFout?为外接晶振功能,所以÷R计数器的分频比为:

NR = (fosc / fR) = (10*106) /200*103 = 50

将50化为二进制数,即就是13位R计数器R0~R12的数码。环路可编程序分频比M

为:

M1 = ( f01 / fR) = ( 960 / 0.2 = 4800

M2 = ( f02 / fR) =(935 / 0.2 = 4675

环路程序分频器采用换模吞除计数方式,所以有:

M = PN+A

的关系。其中N为主计数值,A为吞除脉计数值,P为高速前置分频器的模值,MC145191中P=64。若以M2=4675为例,由上述关系可确知:

N = 73,A = 3,即M = PN+A = 64*73+3 = 4675。

将A=3,N=73化为二进制数值,即就是A0 ~A7、A8 ~A19的数据码值。其他环路分频比的M值均可以用此方法来确定A0 ~ A19这20位数据值,从而实现编程置数。

鉴相器采用PDA,C寄存器的C6=1,鉴相增益KΦ=Ipout/2πA/rad。为得到最大100%的流入流出电流,C寄存器中的C2=C3=1,Rx取18kΩ,PDout流入流出电流约2mA,即KΦ=2*10-32πA/rad。

压控振荡器的压控特性为正向控制特性,所以希望PDout输出正极性,即C7=0,按10%步长变化电流,即C1=0。所以C寄存器中C7~C0为“01001100”控制码状态。

合成器的输出频率在935~960MHz,跨度为25MHz。由上述可知,环路可变分频比在4800~4675范围内变化。显然,这时锁相环路的ζ和ωn也将是可变的,这种变化将直接影响频率合成器的瞬间特性。为保证合成器性能,通常阻尼系数ζ用ζ=0.707来进行环路设计,当然为使环路满足快速换频特性,也可以放宽到≤1来进行设计。ζ=0.707以后,环路的上限频率ωH ≈ ωn。

考虑环路对鉴相波纹的抑制作用,通常要求ωH ≤ ( 1/5)*ωn,

即ωn ≤ ( 1/5*ωR = 0.2 * 2π * 200 * 103(rad/s)。

由于采用PDA鉴相器,环路滤波器接于PDout端口,如图6中所示。环路设计关系为:

KΦKVCO= ωn2MC和2ζ=ωnRC,即:

C = KΦKVCO / ωn2M

R=2ζ/ωnR

式中M取环路可变分频比中心值,

即M = ( 1 / 2)(M1+M2)= ( 1 / 2)(4800+4675) = 4737.5。

所以

有C = (2*10-3/2π*46.7*106)/((1 / 5)*2π*200*103)2 ×4737.5 = 311.42 PF

R=(2*0.707)/(1 / 5)*2π*200*103×311.42×10-12=18.3 kΩ

实践中C可以取330PF,R可取18kΩ接入电路中。

环路锁定时间可以用下式进行估算:

ts = ( 4 / ζ*ωn) = 22.5 μs

考虑是串行送数置数,以及微机指令时间在内,则频率合成器的频率切换时间tp<1ms是完全可以做到的。

电路 电流 电阻 放大器 MCU 电容 CMOS 滤波器 振荡器 电压 相关文章:

- 浅谈E1线路维护技术与应用(01-12)

- R4网络接口和电路域容灾技术(01-05)

- 移动通信网引入IMS的相关探讨(02-21)

- 未来接入网的结构与演进(01-26)

- 电子熔丝在计算机应用中的优势(06-08)

- 高性能、高集成度的TD-SCDMA模拟基带集成电路的实现和应用(01-09)