基于网络处理器的核心路由器设计技术研究

时间:09-17

来源:互联网

点击:

3 基于网络处理器IXP2400的核心路由器体系结构

路由器体系结构的发展经历了四次大的发展,由单机集中式到单机分布式共享总线,再到分布式Crossbar结构,最后到多机互联的集群式结构,目前正朝着系统化、高性能、可扩展方向发展。由于基于网络处理器的路由器体系能够满足这些要求,被公认为推动下一代网络向灵活性和高性能发展的核心技术。Princeton大学的可扩充路由器VERA和Columbia大学的Genesis系统在这方面做了一些推进。前者主要是基于区分服务Diffserv体系结构,注重服务的灵活性和可扩充性;后者基于“Spawn”思想和Netbind机制,注重虚拟网络系统的动态创建,但是两者都没有提出一个通用的体系模型。

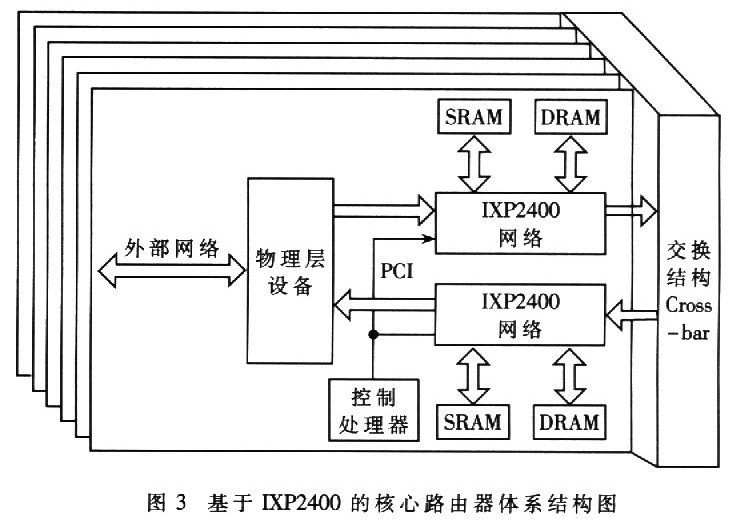

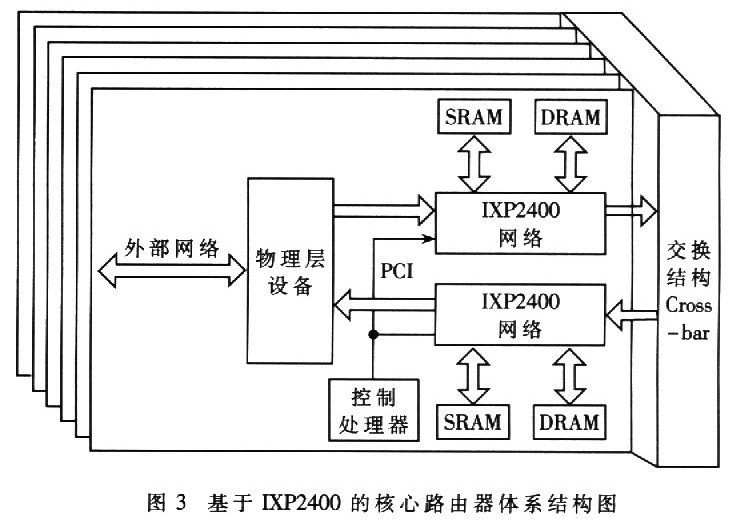

从本质上说,路由器是一种进行网络数据包转发的网络设备,其体系结构可分为三大部分:(1)输入/输出端口;(2)路由计算及处理;(3)交换结构。其中路由计算和处理是路由器的关键,对路由器高性能和灵活性起决定作用。由于网络处理器IXP2400具有高速和灵活性,本文采用IXP2400作为路由计算和处理部分,提出了一种全双工、可扩展的高性能路由器系统体系结构,如图3所示。

在图3中,IXP2400是系统核心部分,负责对数据包进行转发,实现路由功能。SBAM是IXP2400的外接存储设备,通过SBAM Controller与IXP2400连接,主要实现存储数据包处理过程中用到的发送列队、查找表等数据结构。DRAM也是IXP2400外接的存储设备,通过DRAM Controller与IXP2400连接,主要存储数据包和路由表。控制处理器是IXP2400的外接处理器,通过PCIController与 IXP2400连接,主要为系统提供高层的控制和管理功能。物理层设备收发数据包,通过介质和交换接口MSF与IXP2400连接。交换结构作为处理器与外部接口的传输枢纽,对整个系统的性能起着至关重要的作用。它主要分为总线、Cross-bar(纵横制矩阵)和共享内存三种方式。Cross-bar同其他技术相比,具有成本低,可扩展性良好和非阻塞特性,并且可以根据实际需要扩充宽带。

4 基于网络处理器IXP2400的核心路由器系统处理软件模型

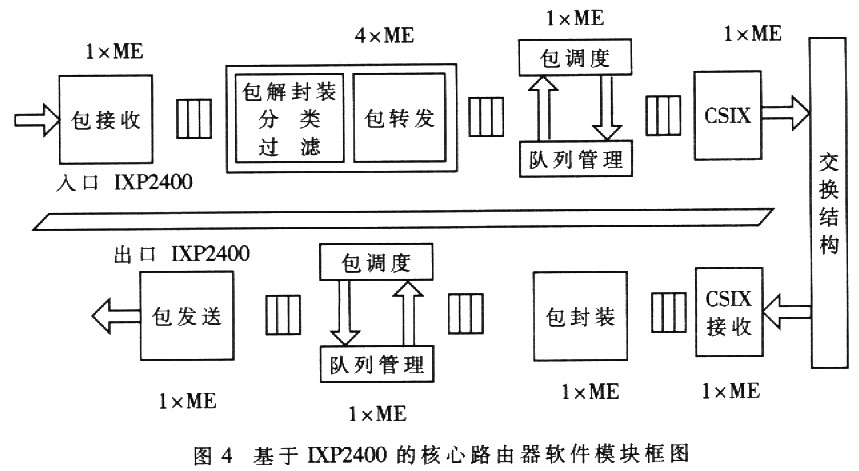

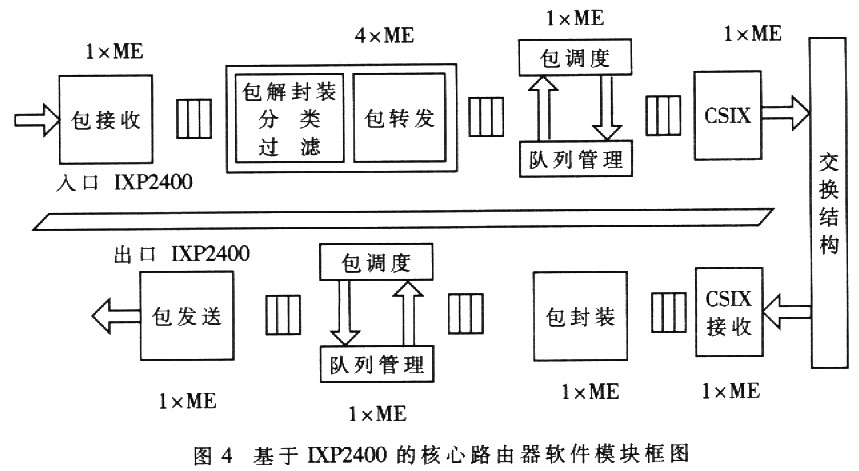

基于IXP2400的核心路由器软件模块框图如图4 所示。入口(Ingress)IXP2400首先通过IXF1104或IXF6048从外部网络接收数据包,然后对数据进行处理,并将处理后的数据通过交换接口芯片发送到交换结构(SF);出口(Egress)IXP2400首先通过交换接口芯片从交换结构接收数据,然后对数据包进行处理,最后通过 IXFll04或IXF6048将数据包发送出去。微引擎的编程模式有流水线模式(HTC)和线程池(POTS)模式,二者各有优缺点。本文采用了HTC 和POTS相结合的编程模式,扬长避短,以取得最佳的处理效率。所有的Context Pipe Stage模块(如包接收、包发送、列队管理等)各自占据一个单独的微引擎,采用HTC方式,每个Context Pipe Stage模块都映射到单独的一个微引擎上。而Funcational Pipeline映射到4个微引擎上,采用POTS方式,执行PPP Decap(数据包解封装)、Classfieation(数据包分类)和IP Forwarding(IP数据包转发)等操作。

如图4所示,系统的数据处理由以下模块组成:

(1)包接收模块。包接收(Packet Rx)模块是一个与低层硬件密切相关的驱动模块。负责接收来自外部网络的数据包分片mpacke,并将mpacket重组得到一个完整的数据包。将重组后的数据包写入DRAM,建立包头信息,Packet Rx模块使用一个微引擎上的8个Thread来进行mpacket包的接收和重组,每个Thread负责处理一个mpaeket 。

(2)解封装/分类/过滤模块。数据包处理模块包括PPP解封装、分类、转发、过滤子模块。这些子模块组成Funeational Pipeline.运行在4个微引擎、32个线程上。PPP解封装子模块通过修改Metadata中的offset和size,将MAC帧头去掉,提取 IP数据帧,实现数据包的解封装功能。分类子模块执行分类操作,将数据包分为IPv4、IPv6和ARP等类型。如果是ARP数据包,将其标记为异常数据包送到Xscale Core作进一步处理;否则,将数据包传送到下一个处理模块处理。

(3)包转发模块。首先检查包头是否符合RFC2460规范。如果不符合,则将该包丢弃;否则,根据IP头进行最长前缀匹配LPM查找,得到Next Hop ID(下一跳ID)、Fabric Blade ID和Output Port三个参数。如果LPM没有找到匹配表项,则将包标记为异常提交给Xscale Core作进一步的处理;否则,根据Next Hop ID进行表查询,获得PPP头信息。将数据包封装为PPP格式之后,Forwarder将包交给DL-QM-Sink模块,该模块判断数据包是否合法,若合法。则向列队管理发送加入队列请求,将数据包加入到相应的发送队列。此外,Forwarder还将修改后的IP头和包描述符Metadata写回 SRAM。

(4)队列管理模块。管理模块是一个运行在单个微引擎的驱动模块,负责利用SRAM Controller中的Q-Array硬件结构对发送队列执行解封装Decap和封装Encap操作。

(5)发送调度模块。模块将处理来自Fabric的流量控制信息、来自QM的队列转换信息和来自MSF的发送状态机。

(6)CSIX发送模块。该模块是位于单个微引擎的驱动模块,接收来自QM发送的消息,对于每次发送请求,微模块将每个Cframer写入发送缓冲TBUF,通过MSF发送状态机发送到Fabric。

(7)CSIX接收模块。接收来自CSIX Fabric的Cframer,并将其重组为IP数据包。

(8)包封装模块。为接收到的信息添加包头,将IP Packet封装为PPP格式,并向队列管理发送加入队列请求,请求将封装后的包加入到相应的发送队列。

(9)出口的队列模块。该模块与信元队列模块的区别在于列队中传递的是分组而不是信元。对于每个出队请求,分组队列模块向调度模块返回一个出队响应消息。

(10)出口包调度模块。出口包调度模块是基于分组的调度,不需要处理来自Fabric的流控信息,出口调度模块对端口进行WRR调度,对每个端口的队列可进行DRR(Deficit Round Robin)调度。

(11)包发送模块。通过媒体介质接口发送分组,将分组分段成mpacket,并写入TBUF,通过MSF状态机进行发送。

本文以Intel IXF2400网络处理器为例,讨论了网络处理器硬件结构和软件开发技术,并在此基础上提出了一种基于网络处理器的路由器体系结构和软件开发流程。在今后几年里,基于网络处理器的路由器将有着非常巨大的发展空间,但其发展也是一个复杂的、长期的过程,将面临严峻的挑战。

路由器体系结构的发展经历了四次大的发展,由单机集中式到单机分布式共享总线,再到分布式Crossbar结构,最后到多机互联的集群式结构,目前正朝着系统化、高性能、可扩展方向发展。由于基于网络处理器的路由器体系能够满足这些要求,被公认为推动下一代网络向灵活性和高性能发展的核心技术。Princeton大学的可扩充路由器VERA和Columbia大学的Genesis系统在这方面做了一些推进。前者主要是基于区分服务Diffserv体系结构,注重服务的灵活性和可扩充性;后者基于“Spawn”思想和Netbind机制,注重虚拟网络系统的动态创建,但是两者都没有提出一个通用的体系模型。

从本质上说,路由器是一种进行网络数据包转发的网络设备,其体系结构可分为三大部分:(1)输入/输出端口;(2)路由计算及处理;(3)交换结构。其中路由计算和处理是路由器的关键,对路由器高性能和灵活性起决定作用。由于网络处理器IXP2400具有高速和灵活性,本文采用IXP2400作为路由计算和处理部分,提出了一种全双工、可扩展的高性能路由器系统体系结构,如图3所示。

在图3中,IXP2400是系统核心部分,负责对数据包进行转发,实现路由功能。SBAM是IXP2400的外接存储设备,通过SBAM Controller与IXP2400连接,主要实现存储数据包处理过程中用到的发送列队、查找表等数据结构。DRAM也是IXP2400外接的存储设备,通过DRAM Controller与IXP2400连接,主要存储数据包和路由表。控制处理器是IXP2400的外接处理器,通过PCIController与 IXP2400连接,主要为系统提供高层的控制和管理功能。物理层设备收发数据包,通过介质和交换接口MSF与IXP2400连接。交换结构作为处理器与外部接口的传输枢纽,对整个系统的性能起着至关重要的作用。它主要分为总线、Cross-bar(纵横制矩阵)和共享内存三种方式。Cross-bar同其他技术相比,具有成本低,可扩展性良好和非阻塞特性,并且可以根据实际需要扩充宽带。

4 基于网络处理器IXP2400的核心路由器系统处理软件模型

基于IXP2400的核心路由器软件模块框图如图4 所示。入口(Ingress)IXP2400首先通过IXF1104或IXF6048从外部网络接收数据包,然后对数据进行处理,并将处理后的数据通过交换接口芯片发送到交换结构(SF);出口(Egress)IXP2400首先通过交换接口芯片从交换结构接收数据,然后对数据包进行处理,最后通过 IXFll04或IXF6048将数据包发送出去。微引擎的编程模式有流水线模式(HTC)和线程池(POTS)模式,二者各有优缺点。本文采用了HTC 和POTS相结合的编程模式,扬长避短,以取得最佳的处理效率。所有的Context Pipe Stage模块(如包接收、包发送、列队管理等)各自占据一个单独的微引擎,采用HTC方式,每个Context Pipe Stage模块都映射到单独的一个微引擎上。而Funcational Pipeline映射到4个微引擎上,采用POTS方式,执行PPP Decap(数据包解封装)、Classfieation(数据包分类)和IP Forwarding(IP数据包转发)等操作。

如图4所示,系统的数据处理由以下模块组成:

(1)包接收模块。包接收(Packet Rx)模块是一个与低层硬件密切相关的驱动模块。负责接收来自外部网络的数据包分片mpacke,并将mpacket重组得到一个完整的数据包。将重组后的数据包写入DRAM,建立包头信息,Packet Rx模块使用一个微引擎上的8个Thread来进行mpacket包的接收和重组,每个Thread负责处理一个mpaeket 。

(2)解封装/分类/过滤模块。数据包处理模块包括PPP解封装、分类、转发、过滤子模块。这些子模块组成Funeational Pipeline.运行在4个微引擎、32个线程上。PPP解封装子模块通过修改Metadata中的offset和size,将MAC帧头去掉,提取 IP数据帧,实现数据包的解封装功能。分类子模块执行分类操作,将数据包分为IPv4、IPv6和ARP等类型。如果是ARP数据包,将其标记为异常数据包送到Xscale Core作进一步处理;否则,将数据包传送到下一个处理模块处理。

(3)包转发模块。首先检查包头是否符合RFC2460规范。如果不符合,则将该包丢弃;否则,根据IP头进行最长前缀匹配LPM查找,得到Next Hop ID(下一跳ID)、Fabric Blade ID和Output Port三个参数。如果LPM没有找到匹配表项,则将包标记为异常提交给Xscale Core作进一步的处理;否则,根据Next Hop ID进行表查询,获得PPP头信息。将数据包封装为PPP格式之后,Forwarder将包交给DL-QM-Sink模块,该模块判断数据包是否合法,若合法。则向列队管理发送加入队列请求,将数据包加入到相应的发送队列。此外,Forwarder还将修改后的IP头和包描述符Metadata写回 SRAM。

(4)队列管理模块。管理模块是一个运行在单个微引擎的驱动模块,负责利用SRAM Controller中的Q-Array硬件结构对发送队列执行解封装Decap和封装Encap操作。

(5)发送调度模块。模块将处理来自Fabric的流量控制信息、来自QM的队列转换信息和来自MSF的发送状态机。

(6)CSIX发送模块。该模块是位于单个微引擎的驱动模块,接收来自QM发送的消息,对于每次发送请求,微模块将每个Cframer写入发送缓冲TBUF,通过MSF发送状态机发送到Fabric。

(7)CSIX接收模块。接收来自CSIX Fabric的Cframer,并将其重组为IP数据包。

(8)包封装模块。为接收到的信息添加包头,将IP Packet封装为PPP格式,并向队列管理发送加入队列请求,请求将封装后的包加入到相应的发送队列。

(9)出口的队列模块。该模块与信元队列模块的区别在于列队中传递的是分组而不是信元。对于每个出队请求,分组队列模块向调度模块返回一个出队响应消息。

(10)出口包调度模块。出口包调度模块是基于分组的调度,不需要处理来自Fabric的流控信息,出口调度模块对端口进行WRR调度,对每个端口的队列可进行DRR(Deficit Round Robin)调度。

(11)包发送模块。通过媒体介质接口发送分组,将分组分段成mpacket,并写入TBUF,通过MSF状态机进行发送。

本文以Intel IXF2400网络处理器为例,讨论了网络处理器硬件结构和软件开发技术,并在此基础上提出了一种基于网络处理器的路由器体系结构和软件开发流程。在今后几年里,基于网络处理器的路由器将有着非常巨大的发展空间,但其发展也是一个复杂的、长期的过程,将面临严峻的挑战。

集成电路 SoC 总线 嵌入式 VxWorks Linux 仿真 相关文章:

- 高性能、高集成度的TD-SCDMA模拟基带集成电路的实现和应用(01-09)

- Vitesse芯片组提升高密度40G/100G光学系统性能(02-25)

- 无线设备中CMOS频率源的应用趋势(05-08)

- 光互连技术(12-29)

- 利用串行RapidIO交换机设计模块化无线基础系统(03-12)

- 基于FPGA的USB接口IP核设计(03-13)