SEP3203处理器的FPGA数据通信接口设计

时间:09-15

来源:互联网

点击:

4 SEP3203与FPGA的数据通信接口设计

数据经FPGA做算法处理后,由SEP3203处理器将结果存储到片外SDRAM中,SDRAM使用的是Winbond公司的W981216BH。硬件实现框图如图6所示。

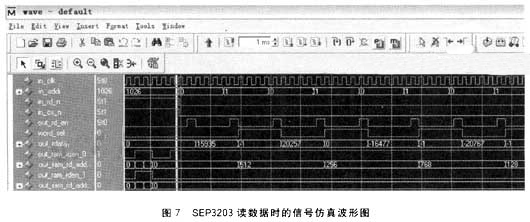

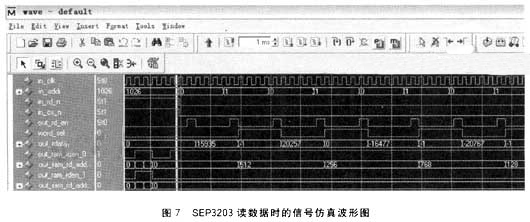

SEP3203对FPGA的访问遵循SRAM时序,图7为SEP3203读数据时的信号仿真波形图。

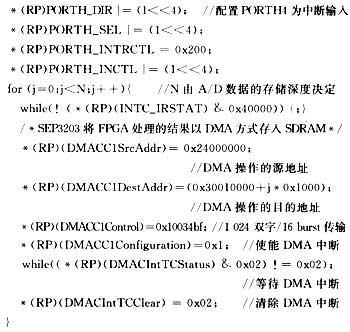

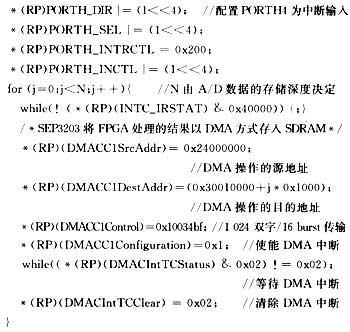

通过DMA方式传输数据时,in_cs_n和in_rd_n信号一直为低,所以只有通过in_addr信号来控制FPGA的内部存储器地址。处理后的A/D数据扩展为32位。

SEP3203处理器默认的AHB总线宽度是32位。当使用DMA传输时,源和目的数据可以是不同的宽度,可以等于或小于总线的物理宽度,DMAC会对数据进行适当的打包和解包,以满足AHB总线宽度。由于FPGA与SEP3202处理器之间只有16位数据总线,所以设计中源地址数据宽度设为16位,目的地址数据宽度设为32位。程序如下:

5 性能分析

为了实现系统的流水线操作,使用了EP1C6Q240C8中的PLL模块。FPGA的外部晶振频率为20 MHz,PLL提供70 MHz的时钟,主要用于A/D数据的处理和结果输出。采集1 024个16位数据的时间为(1/div_clk)×1024,数据从FIFO读入到结果输出的时间为580μs左右,所以当用1.7 MHz以下的频率采样A/D数据时,系统工作正常。若需要更高的A/D采样频率,则可通过优化数据处理过程来实现。

另外,为了提高软件的执行速度,将代码放在SEP3203处理器的eSRAM中执行。它是片上SRAM,实现了单周期数据读/写,可以提供比外存高得多的性能(0.89 MIPS/MHz),极大地缩短了软件执行时间,提高了系统性能。

6 总结

本文给出了SEP3203处理器的FPGA数据通信接口设计,限于篇幅,具体的硬件电路和软件源代码未能详细列出。目前,该系统已在东南大学ASIC中心GE02实验板上调试通过,可以正常工作。

数据经FPGA做算法处理后,由SEP3203处理器将结果存储到片外SDRAM中,SDRAM使用的是Winbond公司的W981216BH。硬件实现框图如图6所示。

SEP3203对FPGA的访问遵循SRAM时序,图7为SEP3203读数据时的信号仿真波形图。

通过DMA方式传输数据时,in_cs_n和in_rd_n信号一直为低,所以只有通过in_addr信号来控制FPGA的内部存储器地址。处理后的A/D数据扩展为32位。

SEP3203处理器默认的AHB总线宽度是32位。当使用DMA传输时,源和目的数据可以是不同的宽度,可以等于或小于总线的物理宽度,DMAC会对数据进行适当的打包和解包,以满足AHB总线宽度。由于FPGA与SEP3202处理器之间只有16位数据总线,所以设计中源地址数据宽度设为16位,目的地址数据宽度设为32位。程序如下:

5 性能分析

为了实现系统的流水线操作,使用了EP1C6Q240C8中的PLL模块。FPGA的外部晶振频率为20 MHz,PLL提供70 MHz的时钟,主要用于A/D数据的处理和结果输出。采集1 024个16位数据的时间为(1/div_clk)×1024,数据从FIFO读入到结果输出的时间为580μs左右,所以当用1.7 MHz以下的频率采样A/D数据时,系统工作正常。若需要更高的A/D采样频率,则可通过优化数据处理过程来实现。

另外,为了提高软件的执行速度,将代码放在SEP3203处理器的eSRAM中执行。它是片上SRAM,实现了单周期数据读/写,可以提供比外存高得多的性能(0.89 MIPS/MHz),极大地缩短了软件执行时间,提高了系统性能。

6 总结

本文给出了SEP3203处理器的FPGA数据通信接口设计,限于篇幅,具体的硬件电路和软件源代码未能详细列出。目前,该系统已在东南大学ASIC中心GE02实验板上调试通过,可以正常工作。

集成电路 嵌入式 ARM FPGA Altera ADI IDT 电路 CMOS 仿真 电压 总线 MIPS 相关文章:

- 高性能、高集成度的TD-SCDMA模拟基带集成电路的实现和应用(01-09)

- Vitesse芯片组提升高密度40G/100G光学系统性能(02-25)

- 无线设备中CMOS频率源的应用趋势(05-08)

- 光互连技术(12-29)

- 利用串行RapidIO交换机设计模块化无线基础系统(03-12)

- 基于FPGA的USB接口IP核设计(03-13)