无电缆测井中大批量数据存储与传输模块的实现

时间:08-31

来源:互联网

点击:

软件设计

软件设计分为两部分,主控单片机的程序设计和日历时钟电路中单片机的程序设计。

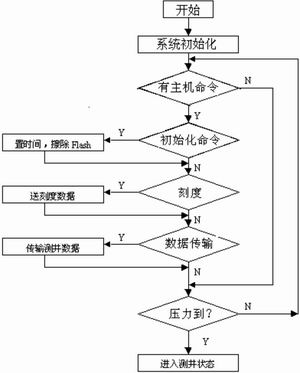

主控单片机程序包括一个主程序和两个中断服务子程序。中断服务程序包含T0中断服务子程序和串口中断服务子程序,其中,T0中断服务予程序只是设定一个中断标志,不做任何其他工作;串口中断服务予程序的主要工作是接收和发送数据。主程序控制整个模块的工作状态,数据存储与传输模块存在两种工作状态,即地面通信状态和井下测井状态,其中,地面通信状态就是在地面与主机相接,和主机之间进行通信,包括初始化(擦除闪存等)、刻度以及数据传输等;而进入井下测井状态后,主要工作是每隔0.5s收集一次井下仪器的测井数据,并将它写入闪存中。主程序框图如图3所示。

图3 主控单片机软件流程

上电复位后,首先进行系统的初始化工作,随后查询主计算机是否发送命令,判断命令类型,根据相应的初始化命令、刻度命令、数据传输命令或者压力到达临界值命令,进行设置时间、 送刻度数据、传输测井数据或者进入测井状态等操作。

日历时钟的软件包含一个主程序和两个中断服务子程序(T0和串行通信),T0中断服务程序主要是设置一个标志,主程序根据此标志进行时间累加,串行通信中断服务子程序主要任务是接收主控单片机的命令,并向主控单片机发送数据。上电后,先进行初始化,初始化后检查是否有T0中断,如果有,则进行时间累加,否则直接检测是否有M301命令,若有,处理命令,否则继续进行检测,命令主要包括初始化命令和传输时间值命令。

结 语

本系统的关键在于地面系统和井下仪器在时间上能够同步,这样就大大提高效率和方便性,实现了无电缆水平井测井,解决了水平井测井成本高的问题。

本系统使用了较少的硬件电路,较少的连线,充分使用了可编程逻辑器件和单片机的内部资源,达到了系统所需的功能和要求,提高了电路的可靠性和工作效率,成本和可维修性都大大高于分立逻辑器件设计模式。 在系统可靠性测试中,误差率在10-9以下。由于井下条件恶劣,因此井下仪器的器件需要选择高温器件。在实地测了多口水平井,取得理想结果。

目前,本系统已在胜利油田测井公司批量生产,在实际的油田测井中,工作稳定可靠,得到了用户单位的好评。

软件设计分为两部分,主控单片机的程序设计和日历时钟电路中单片机的程序设计。

主控单片机程序包括一个主程序和两个中断服务子程序。中断服务程序包含T0中断服务子程序和串口中断服务子程序,其中,T0中断服务予程序只是设定一个中断标志,不做任何其他工作;串口中断服务予程序的主要工作是接收和发送数据。主程序控制整个模块的工作状态,数据存储与传输模块存在两种工作状态,即地面通信状态和井下测井状态,其中,地面通信状态就是在地面与主机相接,和主机之间进行通信,包括初始化(擦除闪存等)、刻度以及数据传输等;而进入井下测井状态后,主要工作是每隔0.5s收集一次井下仪器的测井数据,并将它写入闪存中。主程序框图如图3所示。

图3 主控单片机软件流程

上电复位后,首先进行系统的初始化工作,随后查询主计算机是否发送命令,判断命令类型,根据相应的初始化命令、刻度命令、数据传输命令或者压力到达临界值命令,进行设置时间、 送刻度数据、传输测井数据或者进入测井状态等操作。

日历时钟的软件包含一个主程序和两个中断服务子程序(T0和串行通信),T0中断服务程序主要是设置一个标志,主程序根据此标志进行时间累加,串行通信中断服务子程序主要任务是接收主控单片机的命令,并向主控单片机发送数据。上电后,先进行初始化,初始化后检查是否有T0中断,如果有,则进行时间累加,否则直接检测是否有M301命令,若有,处理命令,否则继续进行检测,命令主要包括初始化命令和传输时间值命令。

结 语

本系统的关键在于地面系统和井下仪器在时间上能够同步,这样就大大提高效率和方便性,实现了无电缆水平井测井,解决了水平井测井成本高的问题。

本系统使用了较少的硬件电路,较少的连线,充分使用了可编程逻辑器件和单片机的内部资源,达到了系统所需的功能和要求,提高了电路的可靠性和工作效率,成本和可维修性都大大高于分立逻辑器件设计模式。 在系统可靠性测试中,误差率在10-9以下。由于井下条件恶劣,因此井下仪器的器件需要选择高温器件。在实地测了多口水平井,取得理想结果。

目前,本系统已在胜利油田测井公司批量生产,在实际的油田测井中,工作稳定可靠,得到了用户单位的好评。

集成电路 电路 总线 振荡器 单片机 51单片机 相关文章:

- 高性能、高集成度的TD-SCDMA模拟基带集成电路的实现和应用(01-09)

- Vitesse芯片组提升高密度40G/100G光学系统性能(02-25)

- 无线设备中CMOS频率源的应用趋势(05-08)

- 光互连技术(12-29)

- 利用串行RapidIO交换机设计模块化无线基础系统(03-12)

- 基于FPGA的USB接口IP核设计(03-13)