一种基于蓝牙射频电路可测性设计的8位逐次逼近型ADC

时间:07-25

来源:互联网

点击:

ADC在蓝牙射频电路中的可测性应用

测试芯片是否符合设计规范有两种方法:即基于构成系统的独立模块级的测试和系统级的测试.本设计综合两者优点,将测试内嵌于接发器架构中,通过一个结构简单,实现容易的ADC,就可完成芯片部分功能的测试.

ADC的应用有两方面:第一用于检测各模块的直流工作点.在电路工作时,高频信号的干扰及其他因素会影响带隙基准源的准确性.一旦偏置电压或偏置电流不准,会直接导致各模块不能正常工作.通过ADC的多通道就能直接检测各模块的直流工作点.第二用于测试一些在高频情况下无法直接测得的性能参数,如信号幅度、噪声等.通过输入简单的激励信号,可以将被测参数转为直流电平,经模数转化后就可方便读出.例如可以用ADC检测蓝牙射频接收通道中的带通滤波器是否符合图3所示的蓝牙协议定义的滤波器的部分指标.将图中特殊点的信号幅度用直流电平表示,通过ADC的模数转换,就可以方便地观测到不同点的衰减是否符合要求.但是,在2MHz和3MHz频率时,信号幅度很小且很接近,给观测带来困难.这种情况可以通过调节自动增益控制,适当增加增益,使信号幅度增大且易于区分,但要求不能使ADC饱和.

图3滤波器性能

测试结果

图4是ADC的芯片照片,该芯片由0.35μm标准CMOS工艺制造,芯片面积是0.5mm×0.3mm.

图4ADC芯片照片

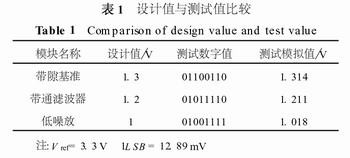

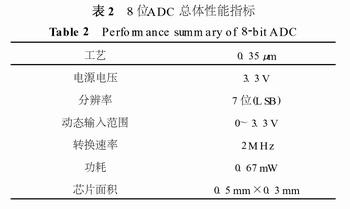

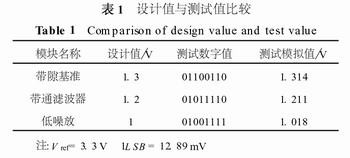

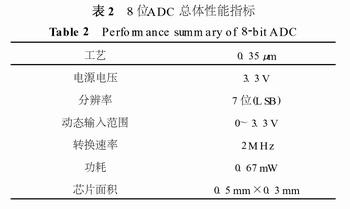

表1给出了蓝牙射频电路中带隙基准源,带通滤波器以及低噪放的理想直流工作电压与经ADC测试到的值,从中可以看到ADC的精度基本达到要求.表2给出了ADC的总体性能指标.

结论

本文设计了基于蓝牙射频电路可测性设计的8位逐次逼近型ADC.芯片测试结果显示,在3.3V工作电压下,ADC的分辨率可达7位.在设计中,输入级采用rail-to-rail结构,利用PMOS差分对和NMOS差分对并联的方法有效提高了电路的共模输入范围.通过对比较器电路和版图的优化设计使失调影响减到最小,大大提高了精度.针对可测性设计的要求,整个电路结构简单,易于实现,与同种功能ADC相比,芯片面积较小,仅0.5mm×0.3mm,功耗也较低.该ADC可以方便地内嵌入蓝牙射频电路的体系结构中,以用于检测各模块电路的部分功能与性能,这样的可测性设计,在使射频电路变得易于测试的同时,也大大减少了测试成本.由于在版图设计中较好地采用了隔离技术,电路在2.4GHz的高频环境下正常工作,表现出了良好的抗干扰能力.另一方面,测试结果显示ADC实际精度为7位,第8位在测试时跳动不确定,造成该结果的原因可能是由于参考电压对地有一定波动并且比较器的输入存在失调.在今后的工作中,将采用比较器的输入失调电压补偿等技术,使得电路和版图进一步优化,从而使结果更理想.同时,怎样更好地利用ADC进行蓝牙射频电路的可测性研究也将成为下一步研究的工作.

测试芯片是否符合设计规范有两种方法:即基于构成系统的独立模块级的测试和系统级的测试.本设计综合两者优点,将测试内嵌于接发器架构中,通过一个结构简单,实现容易的ADC,就可完成芯片部分功能的测试.

ADC的应用有两方面:第一用于检测各模块的直流工作点.在电路工作时,高频信号的干扰及其他因素会影响带隙基准源的准确性.一旦偏置电压或偏置电流不准,会直接导致各模块不能正常工作.通过ADC的多通道就能直接检测各模块的直流工作点.第二用于测试一些在高频情况下无法直接测得的性能参数,如信号幅度、噪声等.通过输入简单的激励信号,可以将被测参数转为直流电平,经模数转化后就可方便读出.例如可以用ADC检测蓝牙射频接收通道中的带通滤波器是否符合图3所示的蓝牙协议定义的滤波器的部分指标.将图中特殊点的信号幅度用直流电平表示,通过ADC的模数转换,就可以方便地观测到不同点的衰减是否符合要求.但是,在2MHz和3MHz频率时,信号幅度很小且很接近,给观测带来困难.这种情况可以通过调节自动增益控制,适当增加增益,使信号幅度增大且易于区分,但要求不能使ADC饱和.

图3滤波器性能

测试结果

图4是ADC的芯片照片,该芯片由0.35μm标准CMOS工艺制造,芯片面积是0.5mm×0.3mm.

图4ADC芯片照片

表1给出了蓝牙射频电路中带隙基准源,带通滤波器以及低噪放的理想直流工作电压与经ADC测试到的值,从中可以看到ADC的精度基本达到要求.表2给出了ADC的总体性能指标.

结论

本文设计了基于蓝牙射频电路可测性设计的8位逐次逼近型ADC.芯片测试结果显示,在3.3V工作电压下,ADC的分辨率可达7位.在设计中,输入级采用rail-to-rail结构,利用PMOS差分对和NMOS差分对并联的方法有效提高了电路的共模输入范围.通过对比较器电路和版图的优化设计使失调影响减到最小,大大提高了精度.针对可测性设计的要求,整个电路结构简单,易于实现,与同种功能ADC相比,芯片面积较小,仅0.5mm×0.3mm,功耗也较低.该ADC可以方便地内嵌入蓝牙射频电路的体系结构中,以用于检测各模块电路的部分功能与性能,这样的可测性设计,在使射频电路变得易于测试的同时,也大大减少了测试成本.由于在版图设计中较好地采用了隔离技术,电路在2.4GHz的高频环境下正常工作,表现出了良好的抗干扰能力.另一方面,测试结果显示ADC实际精度为7位,第8位在测试时跳动不确定,造成该结果的原因可能是由于参考电压对地有一定波动并且比较器的输入存在失调.在今后的工作中,将采用比较器的输入失调电压补偿等技术,使得电路和版图进一步优化,从而使结果更理想.同时,怎样更好地利用ADC进行蓝牙射频电路的可测性研究也将成为下一步研究的工作.

CMOS 蓝牙 射频 电路 ADC DAC 电压 比较器 总线 电路图 电流 仿真 电阻 滤波器 相关文章:

- SoC面临挑战,智能分割顺势而起(11-07)

- PC电源常见故障判断分析与排除 (04-16)

- UWB定位,新一代的精确定位技术(09-20)

- 本土单芯片射频收发器帮助减少TD-SCDMA商用障碍 (11-20)

- TD-SCDMA技术获突破,首颗CMOS单芯片射频芯片完成流片(01-06)

- USB 2.0高速端口的ESD保护(07-28)