SoC面临挑战,智能分割顺势而起

时间:11-07

来源:电子工程专辑

点击:

与数字技术遵循着摩尔定律,以每18个月集成度翻番的步伐进行着"数字革命"相比,模拟技术似乎拖了半导体技术的"后腿",这里可以引入墨菲定律(Murphy’s Law)表述:"任何可能出错的地方,模拟技术必将出错。"

随着半导体工艺逐渐向亚微米、深亚微米切入,SoC成为半导体芯片的一个主流发展趋势,成为减小尺寸、降低成本的首要之选。然而,在ADI一年一度的DoP(Dimensions of Performance)研讨会上,其高速信号处理业务部产品线经理David Robertson指出:"SoC不一定总合适,要考虑性价比、上市时间、投资回报等要求,根据具体情况而定,智能分割更有利于解决SoC面临的一系列问题。"

智能分割浮出水面

根据SoC的复杂性,对于90nm设计来说,开发的费用达到几千万美金,甚至更高。尽管国际上提交继续提高SoC集成度的学术论文达到70%,然而有多少应用可提供一亿美元的开发成本?Robertson表示:"这是一个高风险的事情。SoC的成本包括研发成本和芯片成本,除了手机、PC市场,其他领域可能还没有那么大的量来支撑这些投入。"

集成趋势是由需求量和系统成熟度等共同决定的。在很多情况下,系统的接受度和批量生产并没有增长到换代研发的要求。像手机、PC这样的规模应用适合SoC,而基站、设备和军方的应用中,严格的性能要求导致研发断断续续的完成。

他进一步解释道,以前模拟电路的创新集中在性能更好、有突破性的元器件,如今的挑战变成,如何把ADC等器件放到CMOS中去。在SoC中集成模拟、混合电路存在一定障碍,一方面是为把混合信号集成到电压越来越低的SoC上而做的设计折衷,另一方面模拟、数字在深亚微米的集成会遇到噪声问题。

此外,SoC在方案选择和产品调整的灵活度、转向新工艺的迟滞等方面的弱势,以及网络测试的复杂度、测试硬件成本等因素,都成为选择SoC要面临的挑战。

所以在SoC风靡的今天,ADI提出"SoC不一定总合适","智能分割更有利于解决SoC面临的一系列问题。"

传统分割方法是在数字芯片上集成混合信号前端(MxFE),新的分割方法采用分立的数字芯片ASIC和MxFE,这样做的好处是:不同的工艺、无需折衷的性能、更低的成本,而且降低了对设计者的挑战。例如,典型的调制解调器包括RF/IF线性电路、数据转换器(ADC/DAC)、数字调制解调器三个部分,传统分割方法通常把数据转换器与数字调制解调器做在一起,而智能分割倾向于把RF/IF与数据转换器集成在一起。

WiMAX中的智能分割

"对于正在兴起的WiMAX通讯应用,第一代典型系统应该是用多个芯片开发的,MAC/Moderm部分是FPGA或DSP,射频部分是分离器件如LNA、合成器,然后用ADC/DAC桥接起来。" Robertson谈到,"随着量的增长,为了和更多的RF方案一起应用,数字逻辑经常被集成到专门的ASIC中,在某些情况下,ADC/DAC也集成到这个数字ASIC。"

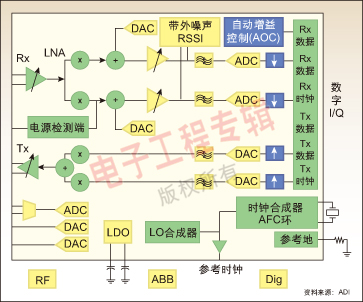

不同于传统的解决方案在独立的器件上实现模拟功能或将数据转换器集成到ASIC上,AD9352和AD9353 RF收发器利用了ADI公司首先提出的"智能分隔"概念,在单芯片内集成了ADC/DAC和RF功能,以及自动校准、自动增益控制、发射功率控制、支持自动频率控制等模拟功能,提供完整的RF和混合信号系统。收发器通过ADI/Q数字I/Q接口与数字调制器直接相连。该数字接口是一种简单的并行CMOS数字I/O接口,现已被多家数字调制器厂商采用。

Robertson称,这有助于数字基带芯片采用先进的CMOS工艺,例如90nm或65nm,而模拟芯片的性能不受影响。同时,内置转换器和智能系统功能降低了对调制器和收发器之间实时信号处理的需求程度,从而大大简化了RF驱动器的开发和支持。

图:AD9352/3 WiMAX射频、模拟基带集成收发器 双频带AD9352工作在2.3-2.7GHz和4.9-5.9GHz频带范围内,而单频带AD9353工作在3.3-3.8GHz频带范围内,覆盖了世界范围内绝大部分获得许可和未经许可的频带。它们集成了一个高灵敏度直接变频CMOS接收器和频带可选基带滤波器。通过集成一个小数N分频的频率合成器提供了一个低相位噪声本地振荡器(LO)通道。另外,为了降低系统成本,内置晶振替代了昂贵的压控温度补偿晶振(VCTCXO)。它们能够提供3.5dB优异的噪声指数,并且邻道功率抑制比(ACPR)比IEEE 802.16标准要求高出8dB,其高线性发射通道提供优良的频谱纯度,发射功率由精确功率检测器检测。"美国目前有很多小的运营商在运行WiMAX网络,而这样小的运营商有几百家,今年夏天最大的一家通讯商Sprint Nextel也宣布采用WiMAX网络,这会进一步增加小运营商的积极性。" Robertson表示应用部署将推动WiMAX的快速发展:"预计2007年应该是WiMAX发展较好的一年。" |

RF SoC ADC DAC CMOS ASIC WiMAX 相关文章:

- 先进的仿真方法简化UWB RFIC设计流程(09-04)

- RF天线开关简化远程信息处理中的无线电(09-12)

- RFID标记技术及其应用(09-27)

- RFID全面挑战蓝牙(09-27)

- Wi-Fi收发器的电源和接地设计(10-22)

- 无线射频技术应用大有作为(02-19)