PLL锁相环的特性、应用与其基本工作过程

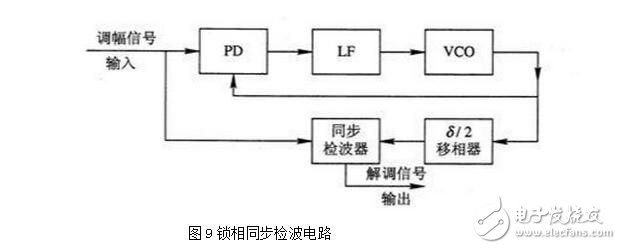

波分量同相的信号,此信号即为本地载波信号,与已调波信号共同加到同步检波器上,才能获得解调信号。

以上是用PLL实现模拟信号的调制与解调,同样可以用PLL实现数字调频、调相信号的调制与解调,最常见的是移频键控(FSK)及移相键控信号的调制与解调。

3、在稳频技术中的应用

利用锁相环路的频率跟踪特性,可实现分频、倍频、混频等频谱变换功能,并从而构成频率综合器与标准频率源。

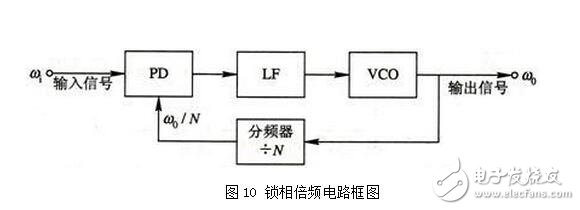

(1)锁相倍频电路

在窄带锁相环路压控振荡器输出到鉴相器的反馈支路中插入一个分频器就得到一个锁相倍频器,如图10所示。

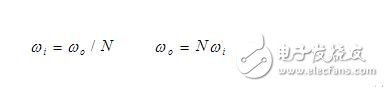

根据锁相原理,当环路输入信号锁定后,鉴相器的两个相位进行比较的输入信号的频率应该相等,即

这样就完成了锁相倍频的任务,倍频次数等于分频器的分频次数。若采用具有高分频次数的可变数字分频器,则锁相倍频电路可做成高倍频次数的可变倍频器。锁相倍频的优点是频谱纯度很纯,且倍频次数可做得很高。

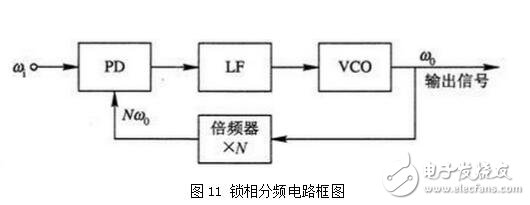

(2)锁相分频电路

如果在基本锁相环路的反馈通道中插入倍频器,就可组成基本的锁相分频电路,如图11所示。

当环路锁定时,鉴相器输入信号角频率wi与压控振荡器经倍频后反馈至鉴相器的信号角频率Nwo应相等,即

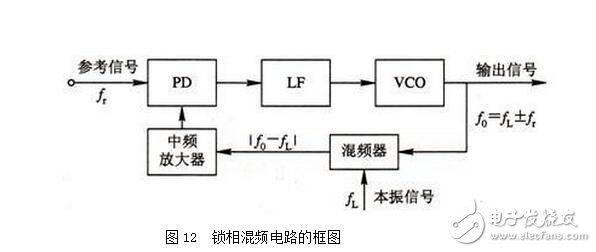

(3)锁相混频电路

锁相混频电路的框图如图12所示。在反馈通道中插入混频器和中频放大器。混频器加入本振信号UL(t),其频率为Lf,因此混频器输出信号的频率为|fo-fL|,经中频放大器放大后加至鉴相器上。当环路锁定时,fr=fo-fL,即fo=fL+fr或fo=fL-fr,这样环路就实现了混频作用。至于fo是fL+fr还是取fL-fr,在环路滤波器带宽足够窄时,取决于VCO输出频率fo是高于还是低于fL,当fo高于fL时,取fo=fL+fr;低于fL时,取fo=fL-fr。

(4)频率合成器(频率综合器)

指能对频率进行加、减、乘、除运算,将一个或几个标准频率变成一系列标准频率信号的设备或装置为频率合成器。频率合成的方法有以下三种:

第一种为直接频率合成法,它是利用混频器、倍频器、分频器及滤波器等来完成频率的加、减、乘、除四种运算。直接式频率合成器的优点是频率变换速度快、相位噪声小,但它的杂波大、硬件设备复杂、体积大、造价高。日前己很少采用。

第二种为锁相式频率合成法,是利用一个或几个锁相环来完成频率变换任务,其特点是体积小,性能好、价格低廉、已获得广泛应用。

第三种为直接数字式频率合成法(DDS),它利用计算机查阅表格上所存储的正弦波的取样值,再通过数模变换来产生模拟正弦信号,改变查表速度就可以变换频率。这种方法实际上是通过对相位的运算进行频率合成的。也可以用计算机求解数字递推关系式等方法来产生正弦信号。除正弦信号外,也能产生其他各种波形的信号。这种方法也称为波形合成法。其优点是体积小、功耗低、性能优良,己超过传统的频率合成技术,这种方法随着计算机技术的不断发展,正获得十分广泛的应用。这里仅简单介绍锁相频率合成器的原理框图。

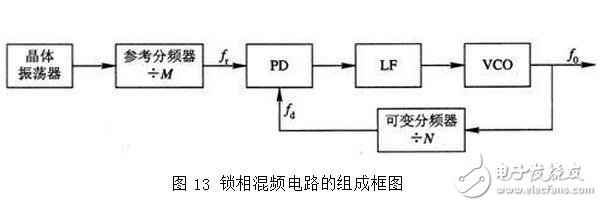

图 13示出单环数字频率合成器的原理框图。

图中可见在基本锁相环路的反馈支路中,接入具有高分频比的可变分频器,分频比为N控制可变分频器的分频比就可得到若干个标准频率输出。为了得到所需的频率间隔,往往在电路中还加一个前置分频器。频率合成器的电路构成和锁相倍频电路是一样的,仅仅分频器采用可变分频器。

其工作原理如下:环路输入来源于高稳定晶体振荡器,当输入参考信号的频率为fr时,环路在锁定后将没有频差,输入频率等于反馈频率,环路输出频率为

可见,只要改变分频比N,就可以改变输出频率。同时,当改变合成器输出频率的间隔,即

为改进单环频率合成器的性能,可以在环路中可变分频器前加入固定分频比的前置分频器,或在反馈支路中加入混频器。

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 全数字锁相环的设计及分析(03-01)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环中YTO自校准技术的应用(10-02)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 锁相环在反馈电路上的应用(01-10)