教你怎么消除影响JESD204B链路传输的因素

时间:09-09

来源:电子技术设计

点击:

所占据的空间。

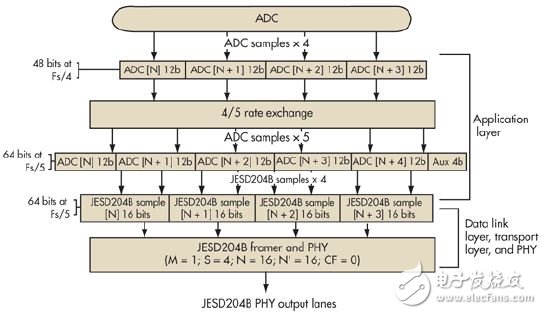

使用上一个问题中的等式进行应用层计算时,需使用有效N’而非实际N’。例如,下文所示的应用层示例中,虽然实际的JESD024B样本N‘参数为16,但可算出ADC样本的有效N‘,因为该例中以64位发送5个样本。因此,Neff = 64/5 = 12.8.由于其他变量保持不变,通道速率将下降20%:

Neff/N’ = 12.8 / 16 = 0.8。

图3. ADC应用层可将5个12位ADC样本重新映射到4个JESD204B N‘= 16样本所用空间中 4位额外辅助信息可提供其他用途

前景如何?

随着JESD204B在数据转换器市场上的不断普及,FPGA平台对知识产权(IP)的保护能力将推动这种趋势。虽然这项技术更为复杂,但由于更多的工程师开始使用JESD204B来设计新系统,未来有关这一话题的讨论还将继续。

- 使用JESD204B同步多个ADC(04-29)

- 合适数据转换器选择:JESD204B与LVDS技术对比(09-15)

- 基于AD9680的宽带高动态全数字雷达接收机设计(10-16)

- IDT打造首款具备JESD204B接口的全新四通道DAC(10-16)

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)