教你怎么消除影响JESD204B链路传输的因素

本、处理、并从器件输出数字信号所需的时间。类似地,DAC的总延迟表示从数字样本数据输入器件直到模拟输出相应样本的时间。通常,对这两者都以分辨率为采样时钟周期进行测量,因为它们与频率有关。这在原理上与JESD204B链路部署中描述的确定延迟的定义有所不同。

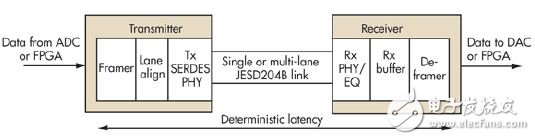

JESD204B链路的确定延迟定义为数据从发送器(ADC或源端FPGA)的并行帧数据输入传播至接收器(DAC或接收端FPGA)并行去帧数据输出所需的时间。该时间通常以分辨率为帧时钟周期或以器件时钟进行测量(图1)。该定义不包括ADC的模拟前端内核或DAC的后端模拟内核。不仅两个器件在这种延迟计算中作为函数使用,与两个器件接口的串行数据信号路由也将作为函数参与计算。这意味着确定延迟在多转换器系统或多点链路中,可能大于或小于确定延迟,具体取决于JESD204B通道的路由长度。接收器的缓冲器延迟有助于弥补路由造成的延迟差异。

图1. 两个互连设备的帧封装器与去帧器之间JESD204B确定延迟的概念示例 延迟函数包括三个项:发送器、接收器和它们之间的接口传播时间

JESD204B如何使用结束位?结束位存在的意义是什么?

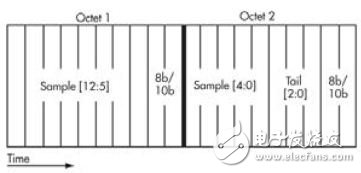

JESD204B链路允许分配多于实际需要的信息空间,用来发送转换器数据和控制位。如果某个特定转换器或配置的数据未填满整个空间,则以定义中的结束位填充。例如,N‘= 16的空间大于打包后的13位实际数据(N = 13 + CS = 0)。这种情况下,将使用3个结束位填充未使用的数据空间(图2)。

图2. 若转换器仅使用13位采样数据,则3个结束位可用于补充N’= 16的第二个8位字

结束位是无信息内容的伪数据位,仅用于完全填充未使用的空间。如果以重复静态值填充结束位,它们可能会产生干扰杂散噪声;但也可用来代表伪随机序列。发送器和接收器都必须根据链路配置了解这些位不含信息,从而接收器可方便地将它们从相关数据流中去除。

我的链路模式没有任何问题,但在正常工作模式下发送器不发送数据。在历代转换器中,低压差分信号(LVDS)和并行接口允许对DAC或ADC的最低有效位(LSB)或最高有效位(MSB)进行简单探测/调试,检查函数转换器是否正在工作。使用JESD204B接口时如何探测MSB或LSB?

这是JESD204B接口的少数几个弊端之一。对LSB或MSB I/O进行电探测以便查看转换器两个方向的链路上是否存在正确的活动并不容易。这是因为,采样数据以通道为单位进行串行化,因此无法轻易电探测特定的加权数据位。然而,如果您希望快速了解转换器是否正在发送或接收任何有效数据(如果确实存在这些数据的话),那么依然可以采用某些方法实现。

某些示波器供应商提供实时数据处理以便串行解码8b/10b数据,并在示波器屏幕上显示未编码数据流。采用这种方法可以探测未加扰数据,从而确定链路上正在进行何种活动。

FPGA供应商提供内部探测软件工具,通过一个USB加密狗将其与计算机相连,为系统设计人员提供一种观察FPGA内发送和接收I/O数据的方法。另外,某些ASIC和转换器提供内部串行回送自测模式,可用于辨认链路上的数据问题。

假设其他链路参数已知,如何计算转换器的通道速率?

如果已知转换器、ASIC或FPGA的其他关键参数,则使用JESD204B的系统设计人员能方便地计算出链路的通道数或通道速率。所有基本链路参数都有如下所示的数学关系,可以据此计算未知变量。根据计算结果,系统设计人员能够在转换器或FPGA限定的架构内选择其他参数,改变链路操作。

通道速率 = (M × N‘× [10/8] × Fs) / L

其中,M表示链路上转换器的数量,N’表示单个样本内信息位的数量(包括样本分辨率、控制和结束位),Fs表示是器件或采样时钟,L表示通道数,通道速率表示单个通道的位速率,10/8表示8b/10b编码的链路开销。

例如,考虑双通道ADC的情况:N‘= 16,Fs = 235 MHz使用两个通道。什么是通道速率?

通道速率 = [2 × 16 × 1.25 × 235 MHz] / 2

通道速率 = 4700 Mbps或4.7 Gbps

什么是应用层,它能做什么?

应用层是JESD204B提供的一种方法,允许样本数据映射到普通规格之外。这对于某些需要传送数据样本尺寸不同于链路N‘的转换器模式而言非常有用。

使用应用层,可将链路上原本通道数较低或通道速率较小的低效率配置变得更为高效。发送器和接收器都需要进行配置才能了解特定的应用层,因为特定的转换器模式会定制或有针对性地对应用层进行设计。图3显示了一个示例,其中5个样本被分配到通常仅能为4个样本

- 使用JESD204B同步多个ADC(04-29)

- 合适数据转换器选择:JESD204B与LVDS技术对比(09-15)

- 基于AD9680的宽带高动态全数字雷达接收机设计(10-16)

- IDT打造首款具备JESD204B接口的全新四通道DAC(10-16)

- 电源管理总线的结构与优势(11-19)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)