解读SAR ADC驱动运算放大器选择

要确定有关的工作条件:所采用的输入时钟频率为9.9968MHz,设定的采样频率为 199.936kSPS;由这两个数值所产生的结果是,ADC 的转换时间为 1.6µs,而采样时间为 3.4µs。因此,对于这个 16 位的转换器而言,我们就需要 12 个时间常数的外部 RC 滤波器来与相应的采集时间匹配。这种条件可将 RC 电路的带宽设置为:

其是:k =12,由此可以实现 562kHz 的带宽。

对于一个低噪声的系统而言,根据实际需要,可以采用尽可能高的带宽。但是,也不要把带宽设置得过高。因为带宽越高,其所允许的噪声也就越高,所以必须在 RC 设定时间和该带宽之间取得一个平衡值。

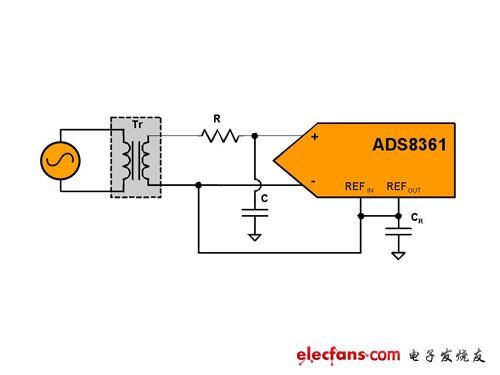

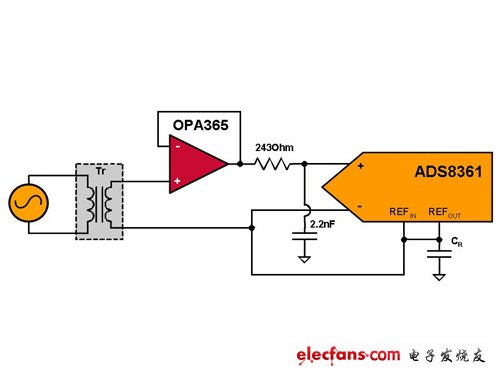

为了确定 RC 滤波器的最佳值,我们曾使用过一个低输出阻抗的信号源。图 8 为用于测量的测试设置。

图 8:通过采用理想的信号源,选择 RC 滤波器

采用这种设置,测量结果不会受到输入缓冲器的影响。值得注意的是,最终计算结果应包括信号源的输出阻抗。在所述示例中,该阻抗为 20Ω。如欲了解测量结果敬请参见图 9-10。

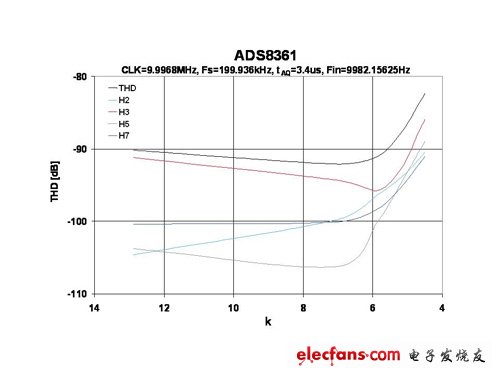

图9:在不同的RC 常数时,测量得出的THD值

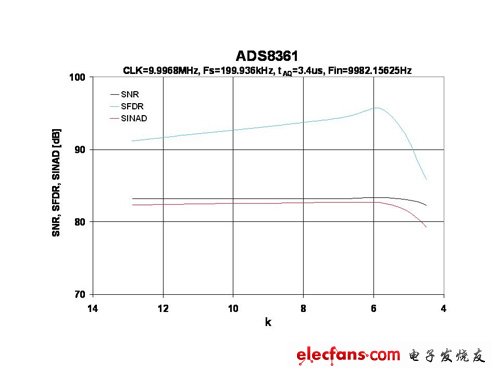

图10:在不同的RC 常数时,测量得出的SNR、SFDR 以及SINAD值

从这些测量结果中,我们发现,当 k = 7 时,可获得最佳的 THD 值;而当 k = 6 时,可获得最佳的 SFDR 值。并且还可以很直观地看出,这些测量结果具有某种意义:因为 k 值越小,RC 滤波器的带宽也就越低,从而降低了噪声。然而,当 k 值变小时,我们发现性能也随之降低。出现这种情况是因为时间常数太大,而且它不能对采样电容器上的输入电压进行相应的设置,从而导致测量误差的出现。

另外,从测量结果中我们还发现,设计程序 (procedure-chosen) 和最佳值之间的性能差异约为 2-3 dB。根据具体的应用情况不同,这种差异也许会很明显,也许会不明显。为什么在设计程序和最佳结果之间会出现差异呢?因为设计程序假定为 ADC 输入采样电容器充电时,出现了最糟糕的情况。因此,为调整时间设定了最保守的数值;而通过测试来实现优化性能,我们经常发现电路的运行条件并非最糟糕的,同时还发现,用于确定设计程序的一些假设必须予以修正。

结论

为了完成信号链的最终性能评估,我们选用当 k = 6.36 或截止频率 = 298kHz 时的 RC 滤波器。在这种前提下,我们采用一只 2.2nF 的COG 型电容器和一只243Ω 的电阻。通过延长采集时间来降低 ADC 的运行速度,具有其它优点:即滤波器的截止频率限制了 ADC 输入信号的有效噪声带宽和运算放大器输出信号的有效噪声带宽。

当采用 ADC 最高的采样速度时,采集时间为 400ns。采用上述相同标准(k = 6.36)时,一阶滤波器的有效噪声带宽为 4MHz。

当采集时间由 400ns 延长至 3.4µs 时,有效噪声带宽则下降为 562kHz。

当选择配置和组件值时,请采用上述测量所得出的结果。图 11为最终调整图。

图11:最终测量调整

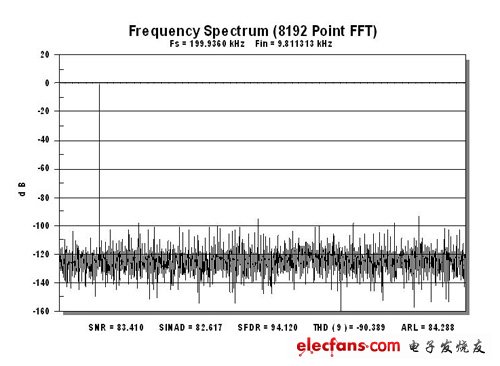

通过对测量结果的比较,我们发现,设计信号链时,此程序是如此的重要。作为参考,我们采用了 ADS8361 产品说明书中的数值。接下来,我们将从测试中获得的结果与 ADC 前端所选用的 RC 滤波器进行比较。从表 2 中我们看出,THD 性能出现了下降的现象,这种下降现象可以归因于信号源(很显然,这并不是用于描绘 ADS8361 特性的同一信号源)。最后需要进行比较的是,从整体解决方案中所得到的测量结果。该解决方案包括具有 RC 滤波器的 OPA365 以及 ADS8361。

表 2 最终测量结果的比较

至此,您可以得出这样的结论:对 ADC 转换器前端的缓冲电路进行合理的设计并不会降低系统的性能。图 12 为整个系统的 FFT 测量结果。

图12:整个信号链的测量结果

结论

我们介绍了 SAR 型 ADC 驱动电路的设计程序,这种驱动电路设计重点旨在运算放大器的要求以及优化运算放大器和 ADC 系统的若干技术。同时,我们还阐述了如何进一步优化 SAR 前端的 RC 电路,但是这些性能调整针对不用的应用而不同,因此,需要对其进行仔细斟酌。另外,我们还发现对 ADC 转换器前端的缓冲电路进行合理的设计并不会降低系统的性能。

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 选择用于无线产品的LED驱动 (11-25)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 利用白光LED驱动器实现低成本高效的氙灯闪光灯驱动(02-21)

- 手持通信设备的光源驱动设计(02-23)