解读SAR ADC驱动运算放大器选择

运算放大器输出级极限

运算放大器的轨至轨运行是指其输入级或输出级,或者是指其输入级和输出级。作为驱动 SAR ADC 输入端的一个缓冲器,我们更关注的是运算放大器轨至轨的输出能力。一般说来,该输出能力表明了输出级能够接近电源轨的程度。该参数可在大多数低频或 DC 输出信号产品说明书中找到,因此更好地了解输出摆幅能力,将有助于在既定条件下驱动 ADC 输入端时,确定最佳工作点。

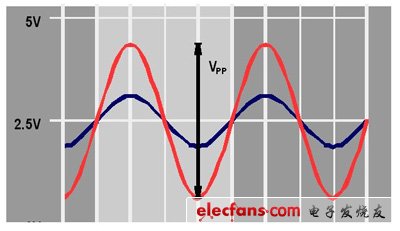

为了确定输出级极限,应事先开展如下测量工作:对于电源电压为 5V 的轨至轨运算放大器来说,输入信号的偏移为 2.5V 或为电源电压的一半。该运算放大器应事先在电压跟随器(或增益为 +1)配置中予以设置。峰至峰输入 AC 信号振幅从0 提高到了 5V,达到了电源电压电平。当输出级达到其极限时,则可以显示出不同的峰至峰输出电压在运算放大器输出端的总谐波失真与噪声 (THD+N) 的测量情况(请参阅图 1)。

图 1:测量得出的运算放大器输出信号

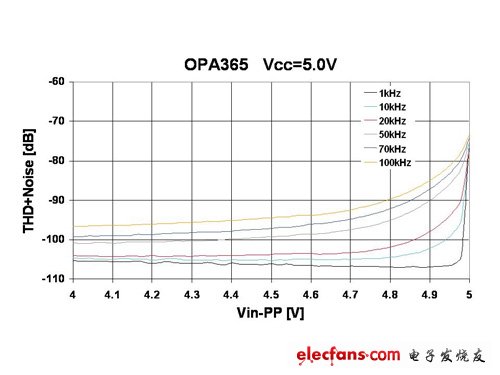

通常情况下,当信号振幅增大时,低频信号 (1kHz)、总谐波失真保持不变。只有当输出电压和电源轨之间的差值低于 10mV 时,才会导致性能显著下降。而当输出信号频率增加时,输出电压和电源电压之间的差值也会随之增大。对于 10kHz 的信号而言,当上述电压差值低于 200mV时,相关性能才开始下降;对于 20kHz 的信号而言,当上述电压差值低于 300mV 时,相关性能才开始下降;以此类推。如果要保持相关性能不变,当频率增大时,则可减小输出信号的摆幅。如欲了解有关的测量结果,敬请参阅图 2。

图2:在不同的输出信号情况下,测量得出的运算放大器失真

考虑到运算放大器的输出级极限,这些测量结果将有助于我们确定 SAR ADC 电路的最佳工作点。正如在上述例子中,采用电源电压为 5V 的 OPA365,在频率为 150kHz,输出信号高达 4.1VPP 时,仍能保持相关的性能不变。由于电源轨留有 450mV 的裕度,所以在 100kHz 的范围内 OPA365 能轻而易举的驱动信号。

RC 负载对运算放大器的影响

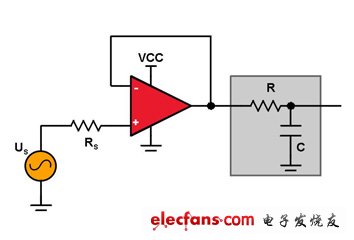

以前,我们曾证实,对于最佳的 AC 性能而言,运算放大器的输出信号摆幅将会介于 450mV 和 4.55V 之间。用于驱动 SAR ADC 运算放大器的第二个重要参数就是要找出其驱动不同的 RC 负载的极限。为此,我们大力推荐在 ADC 输入端采用 RC 滤波器来限制输入噪声的带宽,并帮助运算放大器驱动由 SAR ADC 产生的开关电容负载。图 3 表明了测试调整电路 (test setup circuit) 如何帮助我们确定具有 RC 负载的运算放大器的驱动极限。

图 3:测量运算放大器驱动 RC 负载的能力

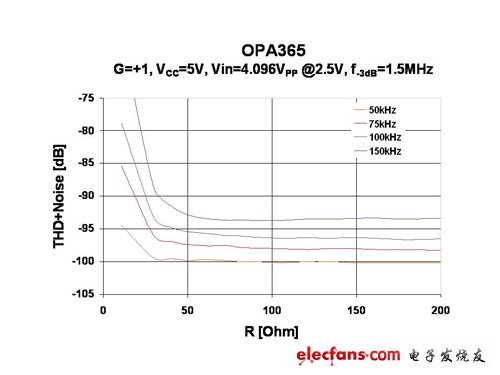

首先,将 RC 电路的截止频率定为 1.5MHz。这一频率限额是以在未来设计中将要采用的 ADC 预期采集时间为基础设定的。另外,如欲保持截止频率不变,则应开展不同 RC 组合以及不同信号频率的测量工作(请参阅图 4)。

图4:在不同的 RC 情况下,测量得出的运算放大器失真情况

对于较低的频率而言,我们则使用较小阻值的电阻或较大容量的电容器。当信号频率增大时,阻值较大的电阻应与容量较小的电容器配合使用,以保持相关性能的稳定。对于在既定条件下的 OPA365 来说,我们发现,通过采用阻值为 50-100Ω 的电阻来改善性能并不令人满意——尤其是对于更高的信号频率而言,想通过采用阻值为 50-100Ω 的电阻来改善性能更是无济于事。对于应用频率 (applied frequency) 而言,我们可以采用阻值大于 100Ω 的电阻或容量小于 1nF 的电容器来保持 AC 性能的稳定。当选择电阻的阻值和电容器的容量时,我们应遵循运算放大器的稳定性要求。

ADC 输入的非线性特性

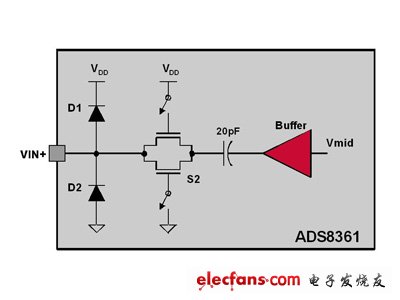

减小输出电压摆幅将有助于保持运算放大器的性能,但还应考虑信号的完整性及其对不同系统组件的影响。随后可向 ADC 输入端发送一个信号。图 5 为常见的SAR ADC 输入级。在流经输入静电放电 (ESD) 保护二极管之后,则可对一个采样电容器和两个场效应晶体管 (FET) 开关中的信号进行采样。如果采用了理想的组件,本设计不会对采样阶段的运算放大器的驱动产生任何影响。

图 5:SAR ADC 的输入级

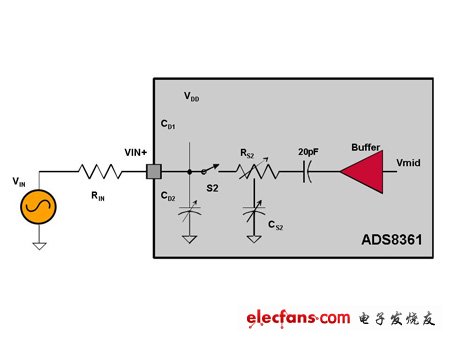

遗憾的是,这些组件并非理想的解决方案(请参阅图 6),特别是临近电源轨的等效负载非线性特性,向缓冲电路提出了新的挑战。

图 6:SAR ADC 的运算放大器等效负载

减小从运算放大器至 ADC 输入端的信号摆幅,将带来诸多益处。在运算放大器的输出端应用 5VPP的信号将减弱总谐波失真 (THD) ,尤其是当频率较高时,更是如此。另外,在 SAR ADC 的输

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 选择用于无线产品的LED驱动 (11-25)

- 基于ISP1581型接口电路的USB2.0接口设计(01-18)

- 单电源供电的IGBT驱动电路在铁路辅助电源系统中的应用(01-16)

- 利用白光LED驱动器实现低成本高效的氙灯闪光灯驱动(02-21)

- 手持通信设备的光源驱动设计(02-23)