功率MOSFET抗SEB能力的二维数值模拟

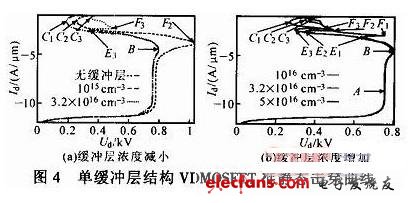

(1)与无缓冲层结构相比,单缓冲层MOSFET的击穿特性曲线多了2个拐点E和F,E点对应n漂移区/n缓冲层高低结击穿电场达到最大,该点称为二次击穿点;之后缓冲层耗尽层扩展,直至n漂移区/n缓冲层界面附近过剩载流子浓度达到缓冲层背景掺杂浓度,这就是F点。

(2)随着缓冲层厚度增加,E,F点间距增大;反之亦然。当缓冲层厚度小到一定程度,E,F点重合。E,F两点重合,可作为厚度优化的一个参考。

(3)随着缓冲层浓度减小,E点向B点移动。当缓冲层浓度低到一定程度,E点与B点重合,F点表观取代B点,此时漂移区过剩载流子浓度达到缓冲层背景掺杂浓度,由于缓冲层浓度高于外延层浓度,从而使负阻转折临界电流IB提高,从3.47x10-5A/μm提高到1.37x10-4A/μm。

(4)随着缓冲层浓度增加,E点向电压负方向移动,C点向电压正方向移动。当缓冲层浓度增加到一定值,E点电位低于C点电位。E点的击穿成为限制器件抗SEB能力的限制因素。因此,对于单缓冲层结构,存在一个最佳缓冲层浓度,由E,C两点电压相等获得。若考虑厚度优化(导通电阻优化),则由C,E,F 3点重合得到一个仿真厚度。

3.3 多缓冲层技术

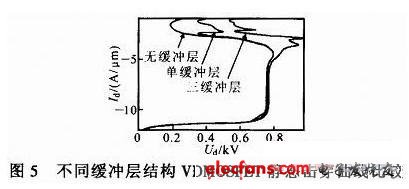

采用缓冲层结构,可改善电场分布,提高器件抗SEB能力。但对单缓冲层结构,优化缓冲层掺杂浓度,或使IB提高,或使Uc达到最佳,无法使两者同时得到改善,有必要采用多缓冲层结构。利用低掺杂浓度缓冲层提高IB,利用高浓度缓冲层提高Uc,这就是多缓冲层技术的思想。

参考单缓冲层浓度优化思想,对三缓冲层结构进行了仿真,结果如图5所示。无缓冲层时,IB=3.47×10-5A/μm,Uc=186 V;单缓冲层时,IB=3.47×10-5 A/μm,Uc=355 V;三缓冲层时,IB=1.03×10-3A/μm,Uc=536 V。可见,与无缓冲层和单缓冲层相比,三缓冲层的IB和Uc均得到了很大改善。

4 结论

缓冲层结构可改善器件抗SEB能力:低掺杂浓度缓冲层有利于提高负阻转折临界电流,高浓度缓冲层更利于提高二次击穿电压。高、低浓度缓冲层结构相结合,可使器件负阻转折临界电流和二次击穿电压均得到改善。根据这一构想,给出一种三缓冲层结构,通过优化掺杂浓度和厚度,使器件抗SEB效应的综合能力提高。仿真结果显示,采用三缓冲层结构,二次击穿电压近似为无缓冲层结构的3倍,负阻转折临界电流提高近30倍。

- DC-DC电荷泵的研究与设计(01-05)

- 从原理到具体电路,深入剖析MOSFET的工作方式(07-06)

- 哪一个更简单,选择热插拔控制器,还是功率MOSFET?(01-23)

- 利用屏蔽栅极功率 MOSFET 技术降低传导和开关损耗(03-31)

- 理解功率MOSFET的电流(11-16)

- IGBT系统电路保护解决方案的设计(04-12)