功率MOSFET抗SEB能力的二维数值模拟

1 引言

功率VDMOSFET晶体管以其开关速度快、输入电阻高、频率特性好、驱动能力高、跨导线性度高等特点,广泛应用在空间系统的电源电路中。但它在空间辐射环境中极易被重离子诱发SEB,造成功率变换器或电源电压的剧烈波动,可导致卫星的电子系统发生灾难性事故。国外对功率VDMOSFET的SEB效应研究较多。而我国起步较晚,在理论和实验上存在许多问题。

在此对功率MOSFET的SEB效应的机理进行了简单分析,并针对600 V平面栅VDMOSFET,利用半导体器件模拟软件Medici研究了缓冲层对提高MOSFET抗SEB能力的影响,提出利用多缓冲层结构改善MOSFET抗SEB能力的方案,最后给出一组优化后的多缓冲层结构。

2 SEB机理以及仿真物理模型

2.1 单粒子烧毁机制

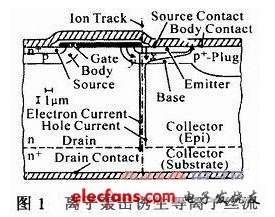

SEB效应主要发生在器件阻断状态,由轰击到MOSFET发生SEB的原理如图1所示。重离子轰击产生的电子空穴对中的电子,在电场作用下向漏接触区(Drain Contact)移动,而空穴则在漏电场作用下沿迹线向p体区(p-body)运动,进入p-body区之后,横向运动,最后经p-body接触区流出。由于横向空穴流产生压降,致使远离电极接触区的p-body部分电位升高,造成p体区/n源极(p-body/n-source)结正偏,触发寄生npn晶体管的发射极向漂移区注入电子。由于此时MOSFET处于高压阻断态,电子的注入会改变空间电荷分布,造成电子在n漂移区/n+衬底(n-drift/n+-sub)高低结的积累,空间电荷区收缩,n-drift/n+-sub高低结处电场强度增加。随着重离子轰击强度增加,等离子体丝流增大,寄生npn晶体管发射结正偏程度增强,n-drift/n+-sub高低结处电场强度越来越高。当该电场增加到一定程度时,会激发雪崩倍增效应,漂移区电流增大,进而使寄生晶体管的发射结进一步正偏,此正反馈效应反复进行,最终可导致器件因电流过大、温度过高而烧毁。

从SEB的失效机理可见,抑制SEB效应可从两方面入手:①降低寄生晶体管的电流增益,削弱晶体管作用,主要包括背栅短路、进行p+注入,增强源区下半导体导电能力、采用源区挖槽工艺,缩短源区宽度、减小寄生晶体管面积等:②优化电场分布,提高n-drift/n+-sub高低结处雪崩倍增效应发生的临界电流。由于这方面的研究相对较少,且主要采用单缓冲层结构,故这里在单缓冲层仿真结果的基础上,提出多缓冲层结构,并给出一组三缓冲层结构的优化结果。

2.2 MOSFET抗SEB能力优化仿真的物理模型

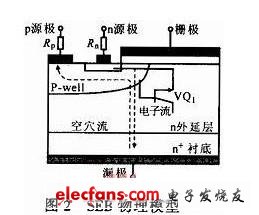

SEB的物理机制和实验结果都表明,功率MOSFET的SEB效应与其寄生晶体管VQ1的导通以及随后器件的二次击穿特性有重要关系,而与入射粒子的种类和剂量无直接关系,重离子的辐射只是一种触发机制。因此,在SEB模型的建立中,可以将入射粒子的影响近似为它所引发的等离子体丝流在源极PN结上的偏压。文献通过将背栅短路的p源极和n源极分开,串联不同的接触电阻(Rp和Rn)来表征这种思想,如图2所示,并经实验研究和仿真验证了该方案的可行性。同时指出,器件的抗SEB能力直接由器件的二次击穿特性决定。二次击穿的电流和电压越高,器件抗SEB能力越好。在此借鉴这种思想,通过器件仿真,明确缓冲层在抗SEB效应中的作用,给出一种三缓冲层的优化结构。

器件仿真中采用了浓度温度相关载流子迁移率模型、SRH复合模型、Auger复合模型以及碰撞离化和禁带变窄模型,暂未考虑热效应。为了更接近实际情况,采用IR 600VN的结构,分别取接触电阻Rp=2.5kΩ,Rn=250Ω。

3 缓冲层提高抗SEB能力的作用

3.1 无缓冲层

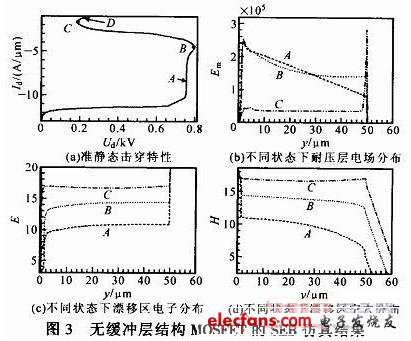

首先对普通无缓冲层MOSFET进行了器件仿真,仿真结果如图3所示,由图可见,器件的静态I-V特性存在3个拐点。

(1)A点对应正常PN结击穿,此时漂移区完全耗尽,空间电荷区载流子浓度近似为本征激发浓度,p-body/n-drift界面处电场最大,达到临界击穿值,如图3b,c所示;

(2)随着漏电流Id的增加,漂移区载流子浓度增加,n-drift/n+-sub高低结附近出现电子积累,该处电场增强,直到电子和空穴的浓度达到背景掺杂浓度,此时漂移区承受的电压达到最高,为B点。Id继续增大,漂移区载流子浓度继续增高,"耗尽层"收缩,电子积累层展宽,漂移区电场降低,器件承受的电压下降,出现"负阻区"。B点电流为负阻转折临界电流IB,该电流越大,进入二次击穿需要的临界辐照强度越高,器件抗SEB能力越强。IB是表征器件抗SEB能力的一个重要标志;

(3)当Id增加到一定程度,n-drift/n+-sub高低结附近电场达到临界击穿电场,发生二次击穿,这就是C点。若C点电压Uc高于器件反向阻断时的工作电压,则器件受辐照后不会诱发二次击穿。因此Uc的高低,也是表征器件抗SEB能力的物理量,Uc越高,器件抗SEB能力越强。改善器件抗辐照能力,就是通过提高IB和Uc来实现。

由图3c,d可见,当出现二次击穿时,漂移区载流子浓度达到1017cm-3,漂移区电场大幅降低,导致Uc很低。如果在衬底与外延层间加一浓度低于此值而高于耐压层的过渡层即缓冲层,缓冲层的耗尽会改变电场分布,缓冲层选择合理,就会使漂移区电场在达到二次击穿时具有较高值,从而改善二次击穿特性,亦即改善抗SEB能力,这就是缓冲层技术的思想。

3.2 单缓冲层技术

对不同单缓冲层浓度下器件的静态击穿特性进行了仿真,仿真结果如图4所示。

- DC-DC电荷泵的研究与设计(01-05)

- 从原理到具体电路,深入剖析MOSFET的工作方式(07-06)

- 哪一个更简单,选择热插拔控制器,还是功率MOSFET?(01-23)

- 利用屏蔽栅极功率 MOSFET 技术降低传导和开关损耗(03-31)

- 理解功率MOSFET的电流(11-16)

- IGBT系统电路保护解决方案的设计(04-12)