理解功率MOSFET的电流

通常,在功率MOSFET的数据表中的第一页,列出了连续漏极电流ID,脉冲漏极电流IDM,雪崩电流IAV的额定值,然后对于许多电子工程师来说,他们对于这些电流值的定义以及在实际的设计过程中,它们如何影响系统以及如何选取这些电流值,常常感到困惑不解,本文将系统的阐述这些问题,并说明了在实际的应用过程中如何考虑这些因素,最后给出了选取它们的原则。

连续漏极电流

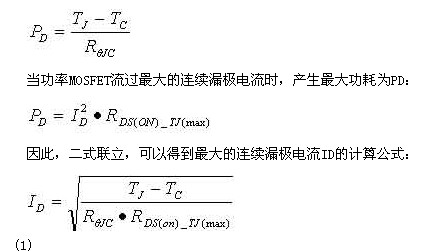

连续漏极电流在功率MOSFET的数据表中表示为ID。对于功率MOSFET来说,通常连续漏极电流ID是一个计算值。当器件的封装和芯片的大小一定时,如对于底部有裸露铜皮的封装DPAK,TO220,D2PAK,DFN5*6等,那么器件的结到裸露铜皮的热阻RθJC是一个确定值,根据硅片允许的最大工作结温TJ和裸露铜皮的温度TC,为常温25℃,就可以得到器件允许的最大的功耗PD:

其中,RDS(ON)_TJ(max) 为在最大工作结温TJ下,功率MOSFET的导通电阻;通常,硅片允许的最大工作结温为150℃。

需要说明的是:上述的电流是基于最大结温的计算值;事实上,它还要受到封装的限制。在数据表中,许多公司表示的是基于封装限制最大的连续漏极电流,而有些公司表示的是基于最大结温的电流,那么它通常会在数据表注释中进行说明,并示出基于封装限制的最大的连续漏极电流。

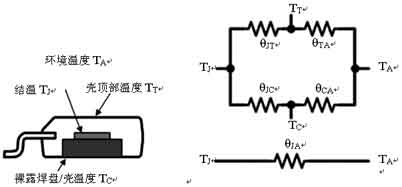

在公式(1)中,需要测量器件的热阻RθJC,对于数据表中的热阻都是在一定的条件下测试的,通常是将器件安装在一个1平方英寸2oz的铜皮的PCB上,对于底部有裸露铜皮的封装,等效热阻模型如图1所示。如果没有裸露铜皮的封装,如SOT23,SO8等,图1中的RθJC通常要改变为RθJL,RθJL就是结到管脚的热阻,这个管脚是芯片内部与衬底相连的那个管脚。

图1 等效热阻模型

功率MOSFET有一个反并联的寄生二极管,二极管相当于一个温度传感器,一定的温度对应着一定的二极管的压降,通常,二极管的压降和温度曲线需要进行校准。

测试时,功率MOSFET的反并联的寄生二极管中通过一定的电流,当器件进入热平衡状态时,测量二极管的压降、器件裸露铜皮或与芯片内部衬底相连的管脚的温度,以及环境温度。

通过二极管的压降和通过的电流,可以计算功耗;通过二极管的压降可以查到结温,根据功耗、结温和器件裸露铜皮或与芯片内部衬底相连的管脚的温度,可以计算得到RθJC或RθJL。根据功耗、结温和环境温度,还可以计算得到RθJA。

特别强调的是,RθJC不是结到器件的塑料外壳温度。RθJA是器件装在一定尺寸的PCB板测量的值,不是只靠器件本身单独散热时的测试值。实际的应用中,通常RθJT+RθJA>>RθJC+RθCA,器件结到环境的热阻通常近似为:RθJA≈RθJC+RθCA

热阻RθJC确定了,就可以用公式(1)计算功率MOSFET的电流值连续漏极电流ID,当环境温度升高时,相应的ID的值也会降低。

裸露铜皮的封装,使用RθJC或RθJA来校核功率MOSFET的结温,通常可以增大散热器,提高器件通过电流的能力。底部没有裸露铜皮的封装,使用RθJL或RθJA来校核功率MOSFET的结温,其散热的能力主要受限于晶片到PCB的热阻。数据表中ID只考虑导通损耗,在实际的设计过程中,要计算功率MOSFET的最大功耗包括导通损耗、开关损耗、寄生二极管的损耗等,然后再根据功耗和热阻来校核结温,保证其结温小于最大的允许值,最好有一定的裕量。

上述计算过程中,ID是基于硅片的最大允许结温来计算的,实际的ID还要受到封装的影响,特别是底部具有裸露铜皮的封装。

封装限制通常是指连接线的电流处理能力。对于额定的连接线的电流限制,常用的方法是基于连接线的熔化温度。当连接线的温度大于220℃时,会导致外壳塑料的熔化分解。在许多情况下,硅电阻高于线的电阻的10倍以上,大部分的热产生于硅的表面,最热的点在硅片上,而且结温通常要低于220℃,因此不会存在连接线的熔化问题。连接线的熔化只有在器件损坏的时候才会发生。

有裸露铜皮器件在封装过程中硅片通过焊料焊在框架上,焊料中的空气以及硅片与框架焊接的平整度会使局部的连接电阻分布不均匀,通过连接线连接硅片的管脚,在连接线和硅片结合处会产生较高的连接电阻,因此实际的连续漏极电流ID会小于数基于结温计算的电流。

基于封装限制的电流是测试的实际工作的最大电流,因此,在数据表中,寄生二极管的电流通常也用这个值表示。

脉冲漏极电流

脉冲漏极电流在功率MOSFET的数据表中表示为IDM,对于这个电流值,许多工程师不明白它是如何定义的。

- DC-DC电荷泵的研究与设计(01-05)

- 从原理到具体电路,深入剖析MOSFET的工作方式(07-06)

- 哪一个更简单,选择热插拔控制器,还是功率MOSFET?(01-23)

- 利用屏蔽栅极功率 MOSFET 技术降低传导和开关损耗(03-31)

- IGBT系统电路保护解决方案的设计(04-12)

- 功率MOSFET抗SEB能力的二维数值模拟(02-07)