ADC 信号调理电路设计——应用背景和电路设计

时间:09-17

来源:ZLG致远电子

点击:

合至模拟电路内。在IC 内部,将硅片焊盘连接到封装引脚的邦定线难免产生线焊电感LPLP 和电阻RPRP,IC 设计人员对此是无能为力的。如果共用地管脚,快速变化的数字电流在B 点产生电压,对于模拟电路无法接受,IC 设计人员意图分开接地管脚,排除此影响。

图2.17 IC 内部模拟与数字地的连接情况

但是,分开之后B 点电压还会通过杂散电容CSTRAYCSTRAY 耦合至模拟电路的A 点。IC封装每个引脚间约有0.2 pF 的寄生电容,是无法避免的。为了防止进一步耦合,AGND 和DGND 应通过最短的引线在外部连在一起,并接到模拟接地层。DGND 连接内的任何额外阻抗将在B 点产生更多数字噪声;继而使更多数字噪声通过杂散电容耦合至模拟电路。

>>> 2.2.6 I/O 扇出电流

由于LPC82x 只有一个电源管脚,即MCU 数字电源与内部ADC 模拟电源共用。虽然这样设计可以在小封装中提供尽可能多的I/O 口,但是对模拟部分会带来干扰问题:MCU工作时在电源上产生数字开关电流,通过共用管脚产生噪声电压,干扰内部ADC。下面的优化建议可以很大程度上避免干扰:

-

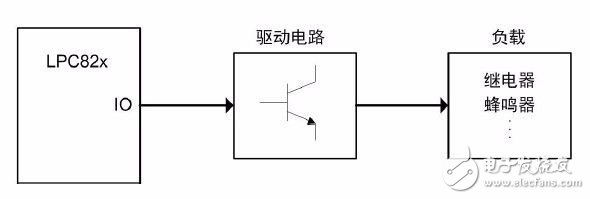

避免I/O 口直接驱动大电流,使用三极管或逻辑芯片间接驱动,详见图2.18;

-

若条件允许,则切换到低功耗模式下执行ADC 采集。

图2.18 使用驱动电路减小I/O 扇出

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)

- 低成本、8通道、同步采样数据采集系统设计(03-11)

- 用于高速 ADC 的串行接口(11-07)

- SAR ADC 掌控世界(03-05)

- 低功耗 ADC:凌力尔特新方法降低整个信号链路的功耗(11-22)

- 怎样采用多种单端信号驱动低功率、1Msps、±2.5V 差分输入、16 位 ADC(03-07)