ADC 信号调理电路设计——应用背景和电路设计

波器,滤除基准源供电3.3V 上可能存在的高频干扰。

1. 低噪声和低输出阻抗

基准电压源芯片使用低成本NCP431,输出噪声10uVpp,输出阻抗0.2Ω。噪声值用于12 位精度已经足够低,但动态输出阻抗0.2Ω 偏大。利用图2.5 中储能或去耦电容C2、C1的低高频阻抗,提供ADC 转换时基准源管脚上的瞬间高频电流,能非常好地解决基准源高频输出阻抗问题。

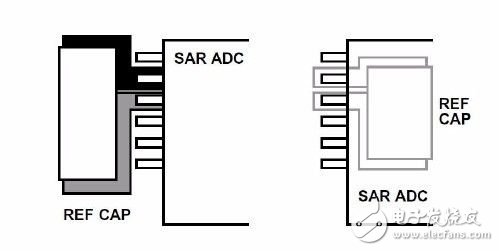

需要注意VREF 管脚上的10uF电容C2 不是旁路电容,而是SAR型ADC 的一部分,这个大电容不适合放在硅片上。在位判断期间,由于各输出位会在数十纳秒或更快的时间内建立,因此该储能电容是用来补充开关电容阵列的,从而与内部电容阵列上已有电荷一起平衡比较器。此大容值储能电容需要满足ADC 位判断建立时间要求。为了降低它的高频ESR,C2 优先选用X5R 材质贴片陶瓷电容,确保靠近基准源管脚VREFP 放置,并且在接近VREFN 模拟地管脚处接地,详见图2.6。

图2.6 VREF 管脚储能电容与芯片在/不在同一面的放置方法

2. 静态工作电流

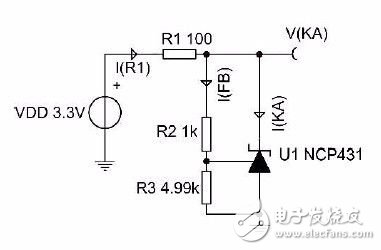

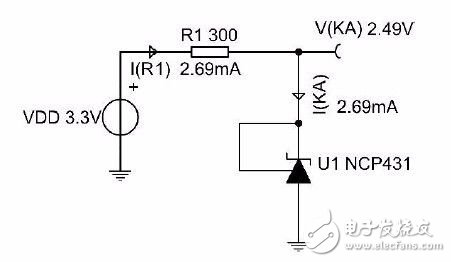

NCP431 是并联型基准,原理类似稳压二极管,只能吸收电流,详见图2.7。在提供负载电流时,维持基准源两端电压不变,使流过限流电阻R1 的总电流不变,调节基准源自身的静态电流减小,使得负载上的电流增加。需计算R1 取值,保证在最大负载电流情况下,有最够的剩余静态电流。

图2.7 并联型的静态工作电流

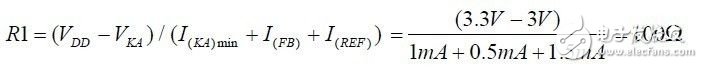

NCP431 手册中的最小静态电流I(KA)min 为1mA,NCP431 输出电压调节电阻R2、R3 所吸收电流I(FB)为0.5mA,LPC82x 的REF 管脚所吸收平均电流I(REF),约为100uA,留出裕量取1.5mA。总的静态电流取3mA,算得决定静态工作电流R1 的阻值:

3. 输出电压选择

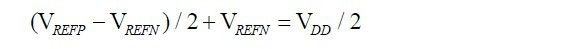

根据LPC82x 手册,为了获得最佳性能,VREFP 和VREFN 应当选择与VDD 和VSS 相同的电压电平。若VREFP 和VREFN 选择不同于VDD 和VSS 的值,则应当确保电压中间值是相同的:

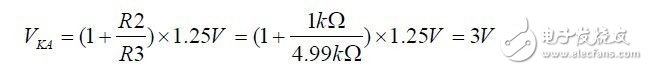

实际测试发现基准电压设置到3.0V 精度最理想,若再升高至接近LPC82x 的电源电压3.3V,因为接近电源轨,ADC 的INL 实测值开始下降,因此标准电路中使用R2、R3 将NCP431的输出电压调整到此值,计算如下:

4. 温漂与直流精度

温漂和初始直流精度是基准源芯片的固有参数,温漂越低初始精度越高,成本越高,温漂25ppm 以下的基准几乎都已经超过LPC82x 芯片自身成本,详见表2.2。

表2.2 基准电压源参数与成本

综合考虑NCP431 是相对合适的选择,它是ONSemi 对TL431 的改进版本,最大温漂由原92 ppm/℃改进为50 ppm/℃,初始准确度优于0.5%。以25℃为参考温度,在-40℃~+85℃范围内,该温漂值引入的误差约为0.3%,基本符合12 位ADC 采集精度的应用。

需要注意标准化电路中R2、R3 影响NCP431 的温漂,应该选择低温漂系数25ppm以下电阻。如果考虑节省成本或者没有可选电阻,为了不影响基准温漂,使用如图2.8 所示的2.5V 输出电路替代。

图2.8 不使用外部电阻的NCP431 基准源电路

基准电压由3V 下降至2.5V 之后,对LPC82x 内部ADC 的INL 会有轻微影响。

>>> 2.2.2 低噪声模拟电源

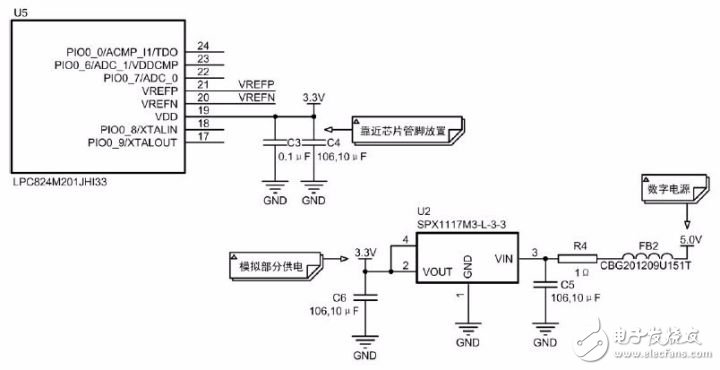

为避免从电源端口串入干扰,需要低噪声的供电电源。利用线性稳压器的纹波抑制比,可以从通常的数字环境开关电源获得此低噪声电源,详见图2.9。

图2.9 低噪声模拟电源电路

使用FB2、R4、C5 所组成的无源滤波网络,可以有效改善1117 在高频段纹波抑制比下降的问题,实现从低频至高频的纹波噪声抑制。其中R3 与C5 形成截止频率1.59KHz 的低通滤波器,使得3.3V 电源上常见的100kHz 以上开关电源纹波干扰衰减10dB 以上。磁珠FB2 在高频时呈现高阻抗,结合C5 在高频时形成更高衰减倍数的低通滤波器,有效滤除3.3V电源上尖峰毛刺噪声。

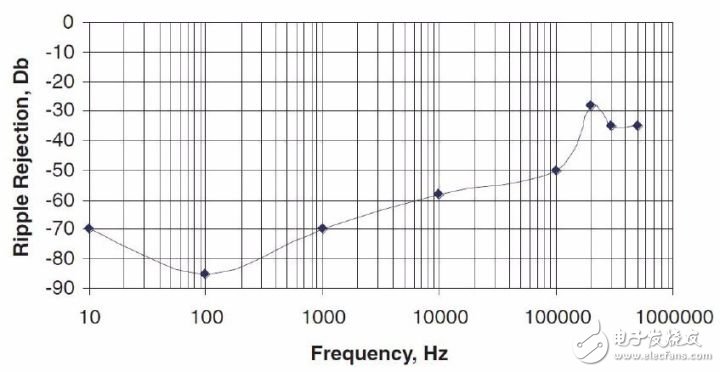

线性稳压器使用SPX1117,纹波抑制比曲线详见图2.10,在低频至10kHz 频段有接近-60dB 的良好纹波抑制比,100kHz 之后快速下降。

图2.10 SPX1117 的纹波抑制比

线性稳压器U2 应该靠近LPC82x 放置,其他数字电路不共用MCU 的3.3V 电源,如果考虑成本需要共用,数字部分电源单独用LC 滤波电路隔离。

>>> 2.2.3 瞬态驱动

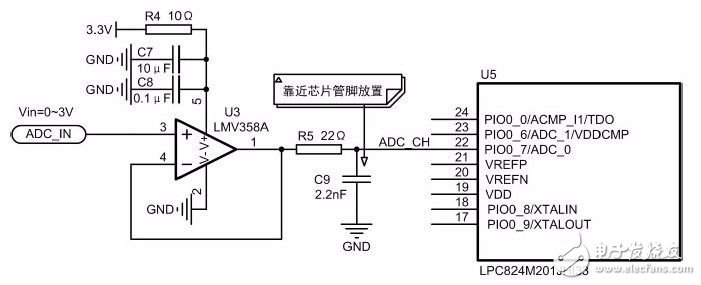

SAR 型ADC 输入端在采样期间具有瞬间充电过程,如果不处理信号源阻抗与内部采样电容的建立时间问题,不管是微处理器中内置的还是外置的ADC,都得不到最好的输出精度。标准化电路中使用运放加RC 组合电路详见图2.11。

图2.11 内部ADC 输入端瞬态驱动电路

通过典型SAR 型ADC 输入端等效电路,有助于理解瞬态驱动电路。如图2.12 所示输入端等效为一个

- 电动 / 混合电动汽车电池管理系统的可靠性(11-09)

- 低成本、8通道、同步采样数据采集系统设计(03-11)

- 用于高速 ADC 的串行接口(11-07)

- SAR ADC 掌控世界(03-05)

- 低功耗 ADC:凌力尔特新方法降低整个信号链路的功耗(11-22)

- 怎样采用多种单端信号驱动低功率、1Msps、±2.5V 差分输入、16 位 ADC(03-07)