数字原理技巧超详细介绍教学

通过本文可以了解时钟信号的数字定时以及诸如抖动、漂移、上升时间、下降时间、稳定时间、迟滞和眼图等常用术语。 本教程是仪器基础教程系列的一部分。

1. 时钟信号

发送数字信号其实发送的就是一串由0或1组成的数字序列。 然而,与不同设备进行通信时,定时信息要与发送的位相关联。 数字波形作为时钟信号的参考。 您可以将时钟信号看成是一个指挥者,它为数字电路系统的各个部分提供定时信号,使每个过程都可在精确的时间点触发。

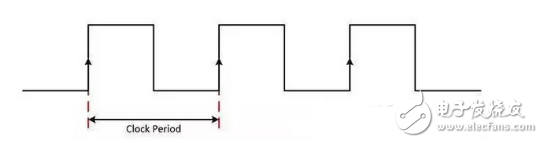

时钟信号是具有固定周期的方波。 周期是指一个时钟边沿到下一个同类时钟边沿之间的时间间隔,最常用的方式是一个上升沿到下一个上升沿之间的时间间隔。 时钟的频率等于时钟周期的倒数。

图1. 数字波形作为时钟信号的参考,时钟信号具有固定周期,在数据传输过程中用固定的时间间隔来同步数字信号发射器和接收器。

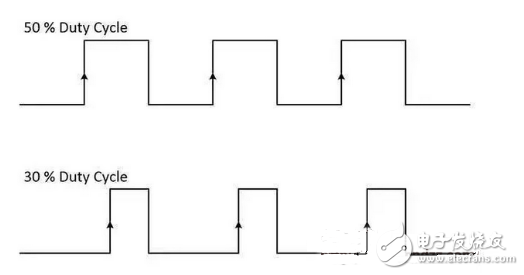

时钟信号的占空比是波形处于所占的时间比。 图2展示了两个具有不同占空比的波形的区别 您可以发现占空比为30%的波形处于的时间少于占空比为50%的波形。

图2.信号的占空比是指波形处于的时间百分比。

时钟信号用于在数据传输过程中同步数字信号发射器和接收器。 比如,发射器可以在时钟信号的每个上升沿发送一个数据位,接收器可使用相同的时钟读取数据。 在这种情况下,设备的确定边沿是上升沿(从低电平到高电平)。 对于其他设备则可能是下降沿(从高电平到低电平)。 时钟的确定边沿又称为有效时钟边沿。 数字信号发射器在每个有效时钟边沿触发新的数据发送,而接收器则在每个有效时钟边沿上进行采样。 后来的设备开始同时使用时钟的上升验和下降沿;这种设备被称为双倍数据速率传输(DDR)设备。 事实上,数据传输对于有效边沿有短暂的短延;这种延时称为时钟到输出时间。

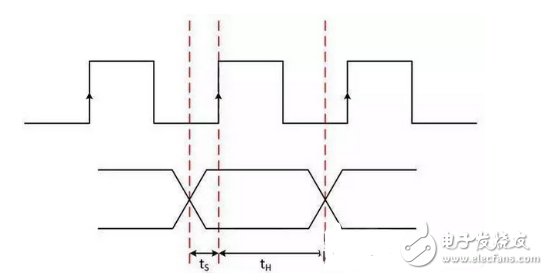

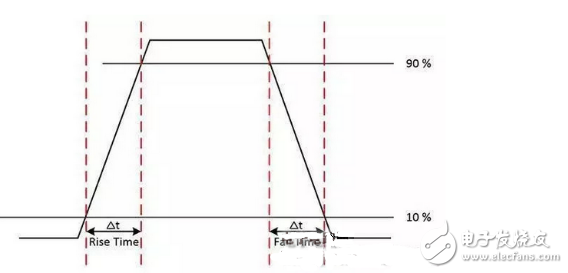

当接收器依据采集时钟接收数据时,我们需要注意两个定时参数,以确保接收数据的可靠性。 建立时间(ts)是指数据连续处于有效逻辑电平且接收器准备好接收输入信号所需的时间。 保持时间(tH)是指接收器采样后,数据发生变化前需要保持在原有状态的时间。 建立时间和保持时间在接收器的时钟有效边沿附近形成了一个稳定的窗口,以便接收器能够可靠地采集数据。 图3给出了一个上升沿时钟信号的建立时间和保持时间。 通常,数字信号会在上升轨迹的中间切换电压;因此时间基准标志通常放置在信号边沿的正中央。

图3.建立时间和保持时间在接收器的时钟有效边沿附近形成了一个稳定的窗口,以便接收器能够可靠地采集数据。

2. 常用术语

在数字电路系统中,定时是最重要的因素之一。 数字通信的可靠性和精确度均取决于定时的质量。 然而,在实际应用中,任何事物都不是理想的。 以下是一些可以帮助您理解特定数字信号定时功能的常用术语和方法。

抖动

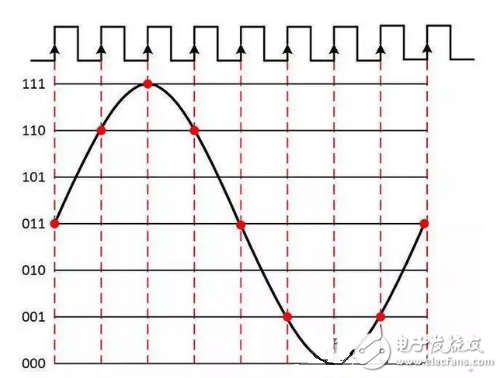

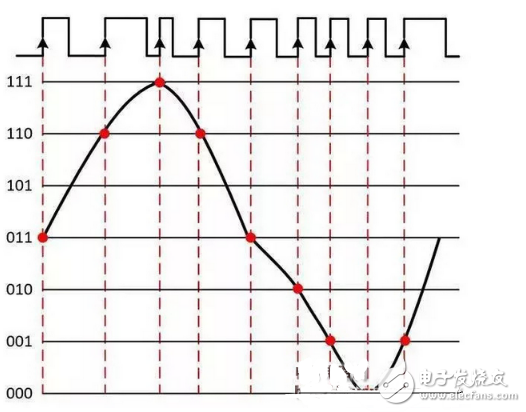

抖动是指事件的理想定时与实际定时之间的偏差。 为了理解这个概念,假设您正在发送一个数字正弦波并在坐标纸上绘制其图形。 每个正方形相当于一个时钟脉冲;由于垂直线之间的间隔是等距的,因此最后我们可以得到一个完美的周期性时钟信号。 在每个时钟脉冲上,您获取3个数据点并将各点绘制在坐标纸上。 由于它具有周期性,因此您得到一个精准的正弦波。

图4. 周期性采样时钟可让数字系统进行正确、精准的通信。

现在,我们假设垂直线之间不是等距的。 这样会使时钟信号的周期性不那么明显。 当您绘制数据时,它们之间的间隔并不相同,因此看起来不正确。

图5. 如果时钟信号发生了抖动,将引起数字波形发生变形。

在图5中,您可以看到时钟信号电平的切换距离是不均匀的;这就是时钟的抖动。 尽管上图抖动较为夸张,但是它说明了抖动的时钟会导致采样在不均匀的时间间隔上触发。 这种不均匀导致要记录和复制的波形发生变形。

现在看看只有1和只有0的数字信号的抖动。 请记住,抖动是指事件的理想定时与真实定时之间的偏差。 请注意单脉冲,抖动是指实际信号边沿定时与理想时间位置的偏差。

图6.单脉冲抖动是边沿定时的偏差

抖动通常从基准信号的过零点处测量。 它通常来自于串扰、同步转换输出和其他定期发生的干扰信号。 抖动会随着时间而发生改变,因此抖动的测量和量化可以是在秒级抖动范围内通过示波器进行目视估算,也可以是按统计学方法进行测量,比如标准差随时间的变化。

漂移

另一个常见的定时问题是漂移。 当发射器的时钟周期与接收器的周期稍有不同时便会发生时钟漂移。 起初,这种漂移影响不大。 然而,随着时间

数字电路 相关文章:

- 数字电路中显示译码器设计的分析与研究(07-12)

- 数字电路设计中部分常见问题解析(01-15)

- 音频专家潘昶:如何进行数码播放器的开发和评估?(02-18)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 数字电路中Multisim10单片机的应用(08-16)

- 步进电机数控解决方案(02-18)