ISE约束导入vivado总共分几步

时间:02-24

来源:网络整理

点击:

最近有些朋友在ISE中做的V7项目需要切换到vivado来,但导入代码后,导入约束时,发现vivado不再支持UCF文件,如果手抄UCF约束到 VIVADO 的 XDC 约束,不仅浪费时间,而且容易出错,这里介绍一种方法可以实现两种约束的切换。

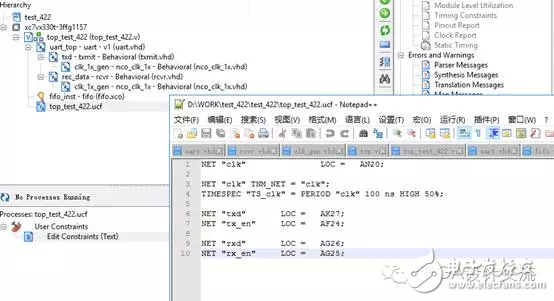

ISE 中的约束是长这个样子的。

导入时会发现无法支持UCF

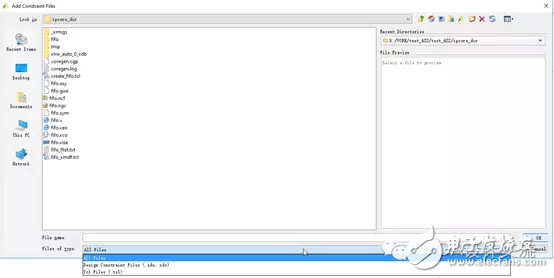

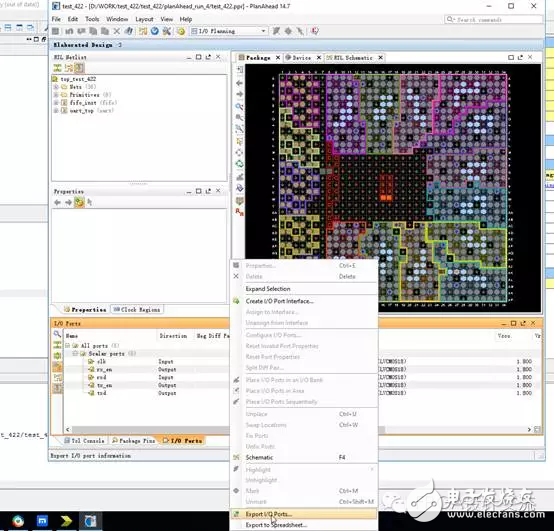

这时,我们可以打开ISE,通过PlanAhead打开图形约束界面,

右键导出约束为CSV格式,并记住导出的路径。

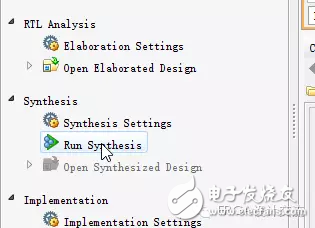

现在可以关闭ISE,然后在vivado中导入代码后,综合一下,

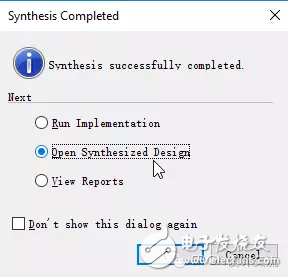

打开综合后的设计,

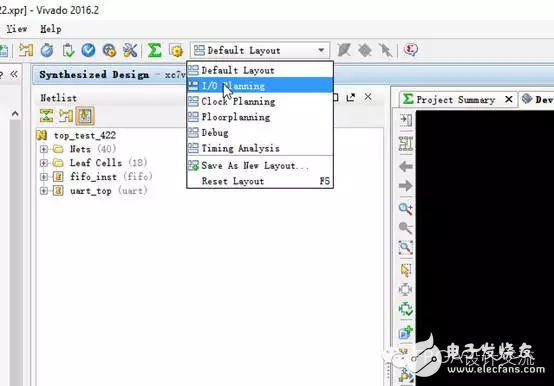

打开IO Planning,

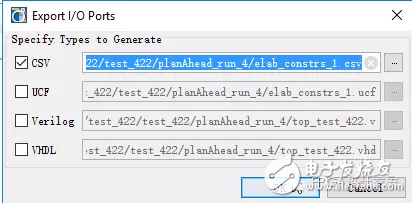

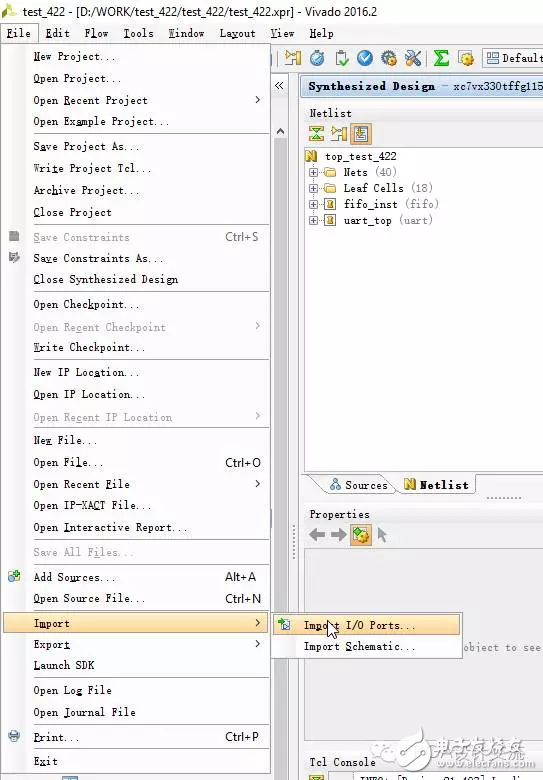

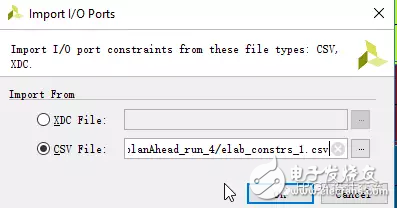

打开文件-》导入IO Ports

指向ISE 导出的csv文件,

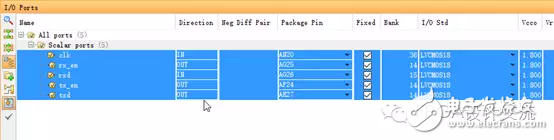

可以看到管脚约束轻松导入!

- 如何利用Vivado HLS处理许多位准确或任意精度数据类型(02-07)

- Vivado环境下如何在IP Integrator中正确使用HLS IP(02-07)

- C++中常用的复合数据类型在Vivado Hls中的应用方法(02-07)

- 使用Vivado HLS创建一个EDK PCore(02-09)

- Zynq交叉编译环境链的建立与C程序编写(02-10)

- 使用VIVADO对7系列FPGA的高效设计心得(02-11)