GRVI Phalanx实现千核处理器

关于GRVI Phalanx ,它是一个大规模并行RISC-V FPGA加速器,由GRVI和Phalanx结合而成。其中GRVI是一个FPGA实现的RISC-V RV32I软处理器核,同时也是手工艺映射和处理元素性能/面积俱最佳的并行处理器。GRVI实现了一个2或3级的单流水线,在Xilinx UltraScale FPGA板卡中消耗320个6-LUT,目前在一个Kintex UltraScale(-2)板卡的内嵌BRAM中按照最佳布局并采用最佳配置时的最高运行频率可达300-375MHz。而Phalanx是一个大规模并行FPGA加速器框架,主要用来减少在开发和管理FPGA加速器时所需付出的消耗和努力。此外Phalanx亦是一个大量软核集群和加速器核的混合物,在具有Hoplite路由的片上网络中可以提供额外的存储和I/O接口。关于GRVI Phalanx的详细信息可以在2016年IEEE第24届国际FCCM研讨会上发表的题为《GRVI Phalanx:A Massively Parallel Risc-V FPGA Accelerator Accelerator》的论文中查看。

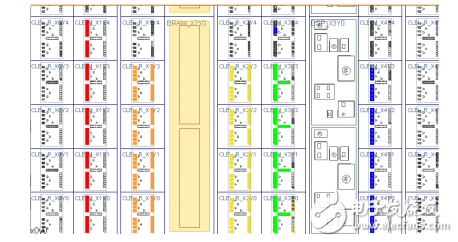

GRVI processing element(PE)datapath RPM

1680个开源ISA RISC-V处理器核于Virtex UltraScale+ VU 9P FPGA运行:

博主Jan Gray近期发表了一片关于千核RISCV处理器的博客,文中提到目前已经可以在Xilinx Virtex UltraScale+ VU9P(是一个中等规模的Virtex UltraScale+ FPGA板卡)板卡上同时并行运行1680个开源的RISC-V处理器核,并成功测试GRVI Phalanx大规模并行加速器框架。据博主所述,这是首例千核RISC-V成功实现运行的应用,同时也是无论使用什么技术在一个芯片上同时运行32bit RISCV核数目最多的应用。

下面是这1680个RISCV核运行在FPGA板卡上的场景图:

这个包含1680个核的GRVI Phalanx不仅是第一个可操作的千核RISC-V,还是第一个运行在FPGA上的上千个32位RISC的核,也是单芯片上可以同时运行32位RISC核数目最多的组合。

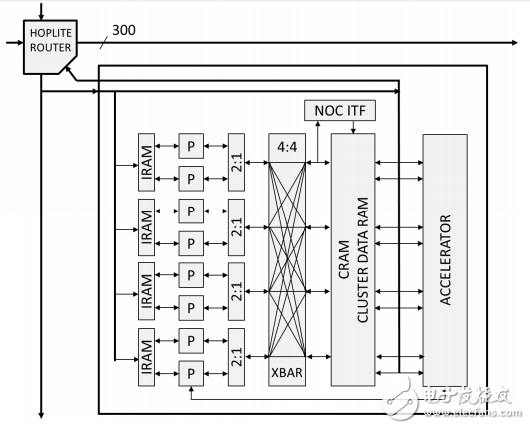

GRVI Phalanx的设计由210个处理器集群组成,每个集群中包含了8个开源的RISC-V处理器核,128KB的多端口RAM,以及一个300-bit的Hoplite NOC路由。下图是一个Phalanx 集群的结构框图:

8 GRVI Cluster and 288-bit payload Hoplite router

不过, 需要注意的是,虽然RISC-V 精简指令集是开源的,且在其官网 还有大量基于RISC-V指令集的开源实现,但是GRVI Phalanx加速框架却不是开源的。

总结:

千核处理器的概念最先是由IBM提出的,同时IBM还研发了具有1025个核的低功耗高性能的微处理器。可见在追求单核运行速度到极致的情况下,现在已经涌现出多核,甚至是千核的并行运算,而在单FPGA芯片上就可以成功运行单核32位的千核处理器,足见Xilinx FPGA的能力不容小觑。

- 高云半导体宣布加入RISC-V基金会(09-18)

- 用大电流LDO为FPGA供电需要低噪声、低压差和快速瞬态响应(08-17)

- 基于FPGA 的谐波电压源离散域建模与仿真(01-30)

- 基于FPGA的VRLA蓄电池测试系统设计(06-08)

- 降低从中间总线电压直接为低电压处理器和FPGA供电的风险(10-12)

- FPGA和功能强大的DSP的运动控制卡设计(03-27)