大唐电信FPGA/CPLD数字电路设计经验分享(5)

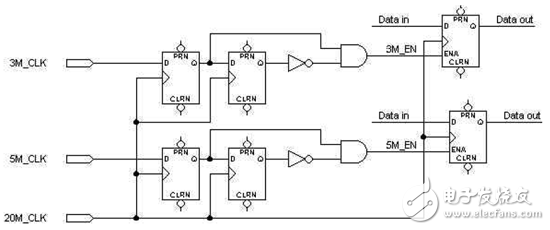

统时钟,输入到所有触发器的的时钟端。3M_EN 和5M_EN将控制所有触发器的使能端。即原来接3M时钟的触发器,接20M时钟,同时3M_EN 将控制该触发器使能 ,原接5M时钟的触发器,也接20M时钟,同时5M_EN 将控制该触发器使能。 这样我们就可以将任何非同源时钟同步化。

图14 同步化任意非同源时钟

(一个DFF和后面非门,与门构成时钟上升沿检测电路)

另外,异步信号输入总是无法满足数据的建立保持时间,容易使系统进入亚稳态,所以也建议设计者把所有异步输入都先经过双触发器进行同步化.

小结:稳定可靠的时钟是系统稳定可靠的重要条件,我们不能够将任何可能含有毛刺的输出作为时钟信号,并且尽可能只使用一个全局时钟,对多时钟系统要注意同步异步信号和非同源时钟。

2.6.6 多时钟系统设计的一些方法:

如果时钟间存在着固定的频率倍数,这种情况下它们的相位一般具有固定关系,可以采用下述方法处理;

使用高频时钟作为工作时钟,使用低频时钟作为使能信号,当功耗不作为首要因素时建议使用这种方式;

在仔细分析时序的基础上描述两个时钟转换处的电路;

如果电路中存在两个不同频率的时钟,并且频率无关,可以采用如下策略:

利用高频时钟采样两个时钟,在电路中使用高频时钟作为电路的工作时钟,经采样后的低频时钟作为使能;

在时钟同步单元中采用两次同步法

使用握手信号

使用双时钟FIFO进行数据缓冲

时钟同步化,如果系统中存在两个时钟clk_a和clk_b,设计者可以使用频率高于max(clk_a,clk_b)两倍的时钟来作为采样时钟,两个低频时钟经过处理后可以作为触发器的使能信号,采用这种方案的好处是整个电路采用单时钟工作,但需要一个额外的高频时钟,当电路有功耗要求时,设计者应该仔细考虑;

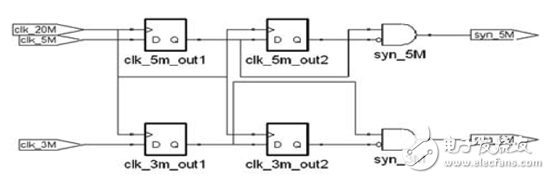

使用20M采样3M和5M,syn_5M作为原来5M信号驱动寄存器的使能信号;

使用高频时钟采样2个低频时钟原理图

使用高频时钟采样2个低频时钟波形图

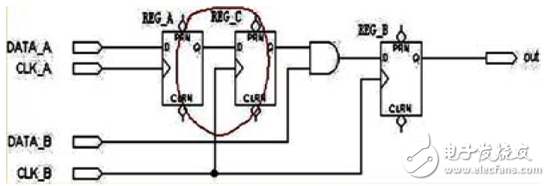

在构件由两个不同系统时钟控制工作的模块之间的同步模块时,应该遵守下面原则:两个采用不同时钟工作的寄存器之间不应该再出现逻辑电路,而应该仅仅是一种连接关系,具体如下图所示,这种方法有利于控制建立保持时间的满足。

握手信号机制是异步系统之间通信的基本方式,我们在处理不同时钟之间的接口时,也可以采用这种方式,但需要注意的是设计者应该仔细分析握手和应答信号有效持续的时间,确保采样数据的正确性。

目前各种器件中提供的双时钟FIFO宏单元很好的提供了对异步双时钟的访问,单元的内部有协调两个时钟的电路,确保读写的正确性。可以利用这个器件完成数据的同步。

1. 采用全局时钟,不要将时钟参与运算。系统提供一定数量的全局时钟线,在布局布线时,尽量满足这些信号的要求以减小时钟偏移和倾斜。如果时序安排不合理使用了较多gated clock,那么这些时钟的偏斜就会较大,不能保障建立时间和保持时间,导致电路工作频率降低或无法工作。

2. 以寄存器为边界划分工作模块。在设计较大规模的电路时,分模块设计是必不可少的,在各模块通过之后再进行系统的联调。但由于在单模块调试和联调时布线资源的占用紧张程度不同,使得每个模块的输出无法保持与单独布线时相同,在联调时造成困难。如果每一个模块的输出端口都采用寄存器输出,那么即使在整体布局布线后,各模块的输出依然可以保证原来的时序,这使得联调的工作效率大大提高。加入这些寄存器也使得电路的可测性有所提高。

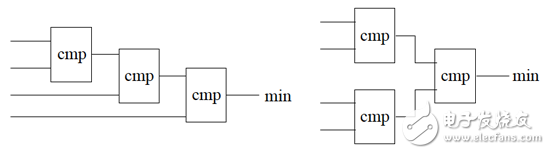

3. 组合逻辑尽量采用并行结构,降低寄存器间组合路径的延迟是提高系统工作频率最主要的手段,因此在完成相同功能的前提下应该尽量使用并行逻辑,如图6所示。

图6 四输入比较器的串行和并行实现

如果没有优先级要求应该尽量采用case语句来描述,这样综合出来的电路并行度要大一些,如果采用if-then-else结构,综合出来的电路都是串行的,增大了时延路径。

4. 在描述中应该消除锁存器,如果某个数据需要保存应该合理安排使用寄存器,因为锁存器在整个工作电平有效期间都对输入敏感,输入中的任何毛刺经过锁存器后都不会消除,这样使得在其后的组合电路发生竞争冒险的可能性大为提高,影响电路性能。一些不适当的描述也会使得产生不必要的锁存器,增加了电路的面积。

5. 在设计中应该尽量采用同步设计,信号被时钟采样后再参与逻辑运算,这样可以隔断组合路径,也可以消除毛刺。在设计中,组合信号的输出不允许反馈作为该组合逻辑的输入,这样可以避免组合环。

- 数字电路中显示译码器设计的分析与研究(07-12)

- 数字电路设计中部分常见问题解析(01-15)

- 音频专家潘昶:如何进行数码播放器的开发和评估?(02-18)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 数字电路中Multisim10单片机的应用(08-16)

- 步进电机数控解决方案(02-18)