Xilinx可编程逻辑器件设计与开发(基础篇)连载25:Spartan

指导原则如下。

只有在NETWORKING 模式下,Bitslip 才有效。其他模式下,不支持Bitslip。

要启动Bitslip 操作,BITSLIP 端口置为High 有效的时间必须持续在一个CLKdiv 周期。在SDR 模式下,Bitslip 的置位时间不能长达两个连续的CLKdiv 周期;在两次Bitslip有效置位之间,Bitslip 的无效时间至少有一个CLKdiv 周期。在SDR 和DDR 两种模式下,从ISERDES 采样到Bitslip 有效的宣称输入到"bit-slipped"ISERDES 的输出Q1-Q6 被

采样到FPGA 内部逻辑,总延迟是两个CLKdiv 周期。

对选通存储器接口的支持。

ISERDES 包含专用电路(包括OCLK 输入引脚),可以完全在ISERDES 模块内部处理选通门到FPGA 跨时钟域的功能。该功能可以极大方便选通存储器的支持,如网络接口、DDR3 接口和QDR 接口。

(2) 输出并串转换器(OSERDES)。

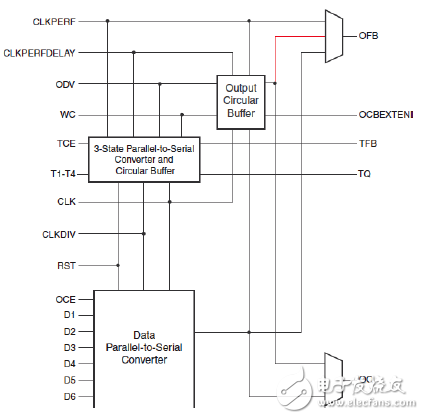

Virtex-6 OSERDES 是专用的并串转换器,用来实现高速源同步接口设计。每个OSERDES 模块包括一个数据串行器和一个实现三态控制的串行器。此转换器支持SDR 和DDR。数据串行化可达6:1(如果使用"OSERDES 宽度扩展"可达10:1)。三态串行化可达4:1。OSERDES 的框图如图5-35 所示。

数据并串转换器。

一个OSERDES 模块中的数据并串转换器接收来自内部逻辑的二到六位并行数据,将数据串行化,然后通过OQ 输出将数据送至IOB。并行数据串行化是按照从数据输入引脚的最低位到最高的顺序进行的(即D1 输入引脚上的数据传输到OQ 引脚的首位)。

OSERDES 使用CLK 和CLKdiv 两个时钟进行数据速率转换。CLK 是高速串行时钟;CLKdiv 是分频并行时钟。

图5-35 OSERDES的结构框图

三态并串转换。

除了数据的并串转换,OSERDES模块还包含一个三态并串转换器,三态并串转换器最多只能串行化四位并行三态信号。三态转换器不能级联。

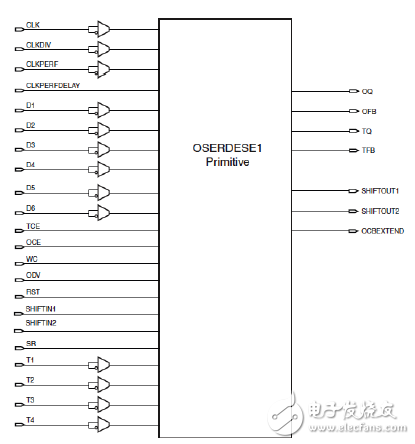

OSERDES的原语如图5-36所示。

图5-36 OSERDES的原语

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)