Xilinx可编程逻辑器件设计与开发(基础篇)连载25:Spartan

式(IDELAY_TYPE=DEFAULT)、固定延迟模式(IDELAY_TYPE=FIXED)、可变延迟模式(IDELAY_TYPE=VARIABLE)和可装载的可变延时模式(IDELAY_TYPE=VAR_LOADABLE)。零保持时间延迟模式允许向后兼容,以使用Virtex-5器件中的零保持时间延迟功能的设计,在这种模式下使用时,不需要例化IDELAYCTRL的原语。在固定延迟模式,延迟值由属性IDELAY_VALUE确定的tap数决定,此值配置后不可更改,此模式必须例化IDELAYCTRL的原语。在可变延迟模式,配置后通过控制信号CE和INC来改变延迟值,此模式必须例化IDELAYCTRL的原语。在可装载的可变延时模式下,IDELAY TAP可以通过FPGA逻辑相连的5位CNTVALUEIN<4:0>装载。当配置为此模式时,也必须例化IDELAYCTRL原语。

IDELAYCTRL延时控制模块。

当IDELAYE1或ISERDES的原语中的IOBDELAY_TYPE属性设置为FIXED、VARIABLE或者VAR_LOADABLE时,都必须例化IDELAYCTRL。IDELAYCTRL模块连续校验IODELAYE1的延时环节,以减少工艺、电压和温度的影响。

(2) OLOGIC资源。

OLOGIC由两个主要模块组成,分别是输出数据通路和三态控制通路。这两个模块具有共同的时钟(CLK),但具有不同的使能信号OCE和TCE。

输出通路和三态通路可独立配置为边沿触发的D型触发器、电平敏感锁存器、异步/组合逻辑或者DDR模式。

组合数据输出和三态控制路径。

组合输出通路用来实现从FPGA内部逻辑到输出驱动器或输出驱动器控制端的直接连接。当FPGA的内部逻辑与输出数据或三态控制之间存在直接(不寄存)连接,或者当"将I/O寄存器/锁存器合并到IOB中"的设置为OFF时,此路径被使用。

输出DDR(ODDR)。

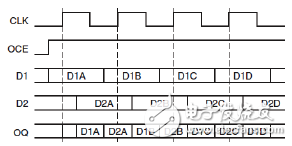

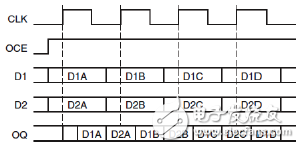

Virtex-6器件的OLOGIC中具有专用寄存器,用来实现DDR功能。要使用此功能,只需要例化ODDR。ODDR只有一个时钟输入,下降沿数据由输入时钟的反相时钟控制。ODDR支持两种操作模式:OPPOSITE_EDGE模式和SAME_EDGE模式。SAME_EDGE模式允许在ODDR时钟的上升沿将两个数据送至ODDR,以节省CLB和时钟资源并提高性能。OPPOSITE_EDGE模式使用时钟的两个沿以两倍吞吐量从FPGA内部采集数据,两个输出都送至IOB的数据输入或三态控制输入。图5-30所示为使用OPPPOSITE_EDGE模式时输出DDR的时序图。图5-31所示为使用SAME_EDGE模式时输出DDR的时序图。

图5-30 OPPPOSITE_EDGE模式时输出DDR

图5-31 SAME_EDGE模式时输出DDR

输出ODDR可以将时钟的一个副本传送到输出。将ODDR原语的D1固定为High,D2固定为Low,时钟与数据ODDR的时钟一样。这个方案可以确保输出数据与输出时钟延时的一致性。

三、 SelectIO的高级特性

除了SelectIO的电器特性和专用于收发SDR或DDR数据的寄存器结构之外,Virtex-6还提供了更高级的逻辑特性。其中包含串并转换器ISERDES、并串转换器OSERDES和Bitslip。

(1) ISERDES。

Virtex-6 ISERDES是专用的串并转换器,具有专门实现高速源同步应用的时钟控制与逻辑功能。图5-32为ISERDES的结构图,其中包括串并转换器(ISERDES)、Bitslip子模块,以及对选通存储器接口的支持,如网络接口、DDR3接口和QDR接口。

图5-32 ISERDES结构图

输入串并转换器。

ISERDES解串器可以实现高速数据传输,不要求FPGA内部资源与输入数据频率匹配。此转换器支持SDR和DDR。在SDR模式下,串并转换器可以实现2、3、4、5、6、7或8bit宽的并行字。在DDR模式下,串并转换器可以实现4、6、8或10位宽的并行字。

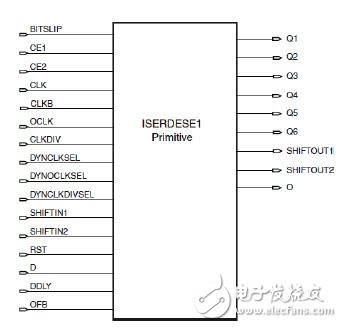

ISERDES的原语ISERDES1如图5-33所示。

图5-33 ISERDES的原语ISERDES1

Bitslip模块。

Virtex-6器件中的所有ISERDES模块都包含一个Bitslip子模块。这个子模块可在源同步网络型应用中实现字对齐。Bitslip对ISERDES模块中的并行数据重新排序,以便将解串器所接收重复串行模式的每种组合都送至FPGA内部逻辑。这种重复串行模式通常称为培训模式(许多网络和电信标准都支持培训模式)。

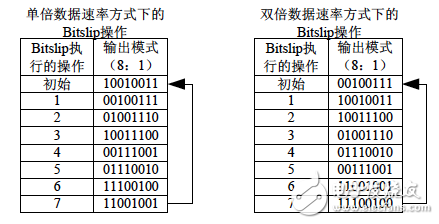

Bitslip操作通过将ISERDES模块的Bitslip引脚置为有效,可以在并行侧对输入串行数据流重新排序。此操作重复进行,直到找到训练模型。图5-34 中所示为SDR 和DDR 模式下Bitslip 操作的效果。为了便于说明,采用了八位数据宽度。Bitslip 操作与CLKdiv 同步。在SDR 模式下,每次Bitslip 操作使输出模式左移一位。在DDR 模式下,每次Bitslip

操作使输出模式在右移一位和左移三位之间交替变化。在此示例中,输出模式在第八次Bitslip 操作时还原到初始模式。这里假定串行数据是八位重复模式。

图5-34 Bitslip 操作

使用Bitslip 子模块的

- 可编程逻辑控制器(PLC)基本操作及功能简介(03-07)

- 基于可编程逻辑器件的数字电路设计(10-16)

- 基于CPLD的机载雷达控保系统设计与实现(10-29)

- 德州仪器可编程逻辑和自动化控制器(PLC/PAC)解决方案(11-03)

- 基于Xilinx(赛灵思) CPLD的看门狗电路设计(10-09)

- 莱迪思技术专家分享:基于FPGA的视频监控时代(02-21)