Nexys3学习手记7:MicroBlaze小试牛刀

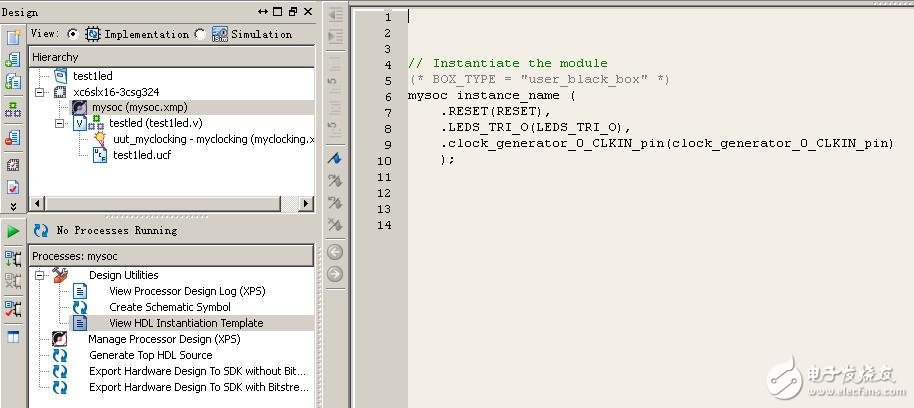

图14 生成系统例化模板 将此模板复制到ISE顶层源代码中,相应匹配好接口,原先的8个LED接口将由软件编程控制。顶层源代码修改如下:module testled( clk,rst_n, led ); input clk; //100MHzinput rst_n; //低电平复位信号 output[7:0] led; //连接到LED指示灯 wire clk_100m; //clocking输出100MHzwire clk_50m; //clocking输出50MHzwire clk_25m; //clocking输出25MHzwire clk_12m5; //clocking输出12.5MHzwire clk_locked; //clocking输出完成标志位 //---------------------------------------------------//IP核Clocking Wizard例化//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG myclocking uut_myclocking (// Clock in ports .CLK_IN1(clk), // IN // Clock out ports .CLK_OUT1(clk_100m), // OUT .CLK_OUT2(clk_50m), // OUT .CLK_OUT3(clk_25m), // OUT .CLK_OUT4(clk_12m5), // OUT // Status and control signals .RESET(!rst_n),// IN .LOCKED(clk_locked)); // OUT// INST_TAG_END ------ End INSTANTIATION Template --------- //---------------------------------------------------// 例化mysoc系统(* BOX_TYPE = "user_black_box" *)mysoc uut_mysoc ( .RESET(rst_n), .LEDS_TRI_O(led), .clock_generator_0_CLKIN_pin(clk_100m) ); endmodule 最后我们双击"Generate Programming File"完成硬件系统的编译和下载文件生成。 下一步我们把平台转移到SDK,在工程目录下新建一个名为SDK_workspace的文件夹,然后打开SDK时需要选择一个workspace,如图15所示,对应定位到SDK_workspace文件夹下即可。

图14 生成系统例化模板 将此模板复制到ISE顶层源代码中,相应匹配好接口,原先的8个LED接口将由软件编程控制。顶层源代码修改如下:module testled( clk,rst_n, led ); input clk; //100MHzinput rst_n; //低电平复位信号 output[7:0] led; //连接到LED指示灯 wire clk_100m; //clocking输出100MHzwire clk_50m; //clocking输出50MHzwire clk_25m; //clocking输出25MHzwire clk_12m5; //clocking输出12.5MHzwire clk_locked; //clocking输出完成标志位 //---------------------------------------------------//IP核Clocking Wizard例化//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG myclocking uut_myclocking (// Clock in ports .CLK_IN1(clk), // IN // Clock out ports .CLK_OUT1(clk_100m), // OUT .CLK_OUT2(clk_50m), // OUT .CLK_OUT3(clk_25m), // OUT .CLK_OUT4(clk_12m5), // OUT // Status and control signals .RESET(!rst_n),// IN .LOCKED(clk_locked)); // OUT// INST_TAG_END ------ End INSTANTIATION Template --------- //---------------------------------------------------// 例化mysoc系统(* BOX_TYPE = "user_black_box" *)mysoc uut_mysoc ( .RESET(rst_n), .LEDS_TRI_O(led), .clock_generator_0_CLKIN_pin(clk_100m) ); endmodule 最后我们双击"Generate Programming File"完成硬件系统的编译和下载文件生成。 下一步我们把平台转移到SDK,在工程目录下新建一个名为SDK_workspace的文件夹,然后打开SDK时需要选择一个workspace,如图15所示,对应定位到SDK_workspace文件夹下即可。

Nexys3 MicroBlaze 相关文章:

- Nexys3学习手记3:硬件外设走马观花(02-11)

- Nexys3学习手记5:流水灯在线运行(02-11)

- Nexys3学习手记6:ClockingWizard探秘(02-11)

- Nexys3学习手记8:FT232之高速UART(02-11)

- Nexys3学习手记2:建立自己的开发环境(02-11)

- MicroBlaze:malloc 函数动态分配内存溢出(02-11)